FPGA - ZYNQ 基于Axi_Lite的PS和PL交互-程序员宅基地

技术标签: fpga开发

前言

在FPGA - ZYNQ 基于EMIO的PS和PL交互中介绍了ZYNQ 中PS端和PL端交互的开发流程,接下来构建基于基于Axi_Lite的PS和PL交互。

开发流程

Axi_Lite从机

在FPGA - AXI4_Lite(实现用户端与axi4_lite之间的交互逻辑)中,详解介绍了AXI4总线,以及AXI_LITE端口信号及其功能,其中axi4_lite 读写过程框架图中介绍了axi4_lite主机搭建过程。

接下来构建axi4_lite从机

Axi4_lite端口信号及其功能

根据axi_lite读写信号分析:

在这里我们需要构建axi4lite_slave和user_ram。

axi4lite_slave:

`timescale 1ns / 1ps

module axilite_slave #(

parameter USER_WR_DATA_WIDTH = 32 , //用户写数据位宽和AXI4―Lite数据位宽保持一致

parameter USER_RD_DATA_WIDTH = 32 , //用户读数据位宽和AXI4―Lite数据位宽保持一致

parameter AXI_DATA_WIDTH = 32, //AXI4_LITE总线规定,数据位宽只支持32Bit或者64bit

parameter AXI_ADDR_WIDTH = 32

)(

input axi_clk,

input reset,

output reg s_wr_vld,

output reg [USER_WR_DATA_WIDTH-1:0] s_wr_data,

output reg [AXI_ADDR_WIDTH-1 :0] s_wr_addr,

output reg s_rd_addr_vld,

output reg [AXI_ADDR_WIDTH-1 :0] s_rd_addr,

input [USER_RD_DATA_WIDTH-1:0] s_rd_data,

input s_rd_data_vld,

input [AXI_ADDR_WIDTH -1:0] s_axi_awaddr, //axi write address channel

input [2:0] s_axi_awprot,

input s_axi_awvalid,

output reg s_axi_awready,

input [AXI_DATA_WIDTH-1:0] s_axi_wdata, //axi write data channel

input [AXI_DATA_WIDTH/8-1:0] s_axi_wstrb,

input s_axi_wvalid,

output reg s_axi_wready,

output [1:0] s_axi_bresp, //axi wirte response channel

output reg s_axi_bvalid,

input s_axi_bready,

input s_axi_arvalid, // axi read address channel

output reg s_axi_arready,

input [AXI_ADDR_WIDTH-1:0] s_axi_araddr,

input [2:0] s_axi_arprot,

output reg [AXI_DATA_WIDTH-1:0] s_axi_rdata, // axi read data channel

output [1:0] s_axi_rresp,

output reg s_axi_rvalid,

input s_axi_rready

);

(* dont_touch="true" *) reg a_reset_sync_d0;

(* dont_touch="true" *) reg a_reset_sync_d1;

(* dont_touch="true" *) reg a_reset_sync;

/*------------------------------------------*\

状态机信号定义

\*------------------------------------------*/

reg [1:0] wr_cur_status;

reg [1:0] wr_nxt_status;

reg [1:0] rd_cur_status;

reg [1:0] rd_nxt_status;

localparam WR_IDLE = 3'b000;

localparam WE_DATA = 3'b001;

localparam WR_BRESP = 3'b010;

localparam RD_IDLE = 3'b000;

localparam RD_PRE = 3'b001;

localparam RD_DATA = 3'b010;

/*------------------------------------------*\

assign

\*------------------------------------------*/

assign s_axi_bresp = 0;

assign s_axi_rresp = 0;

/*------------------------------------------*\

CDC

\*------------------------------------------*/

always @(posedge axi_clk) begin

a_reset_sync_d0 <= reset;

a_reset_sync_d1 <= a_reset_sync_d0;

a_reset_sync <= a_reset_sync_d1;

end

/*------------------------------------------*\

AXILITE从机写过程

\*------------------------------------------*/

always @(posedge axi_clk) begin

if (a_reset_sync)

wr_cur_status <= WR_IDLE;

else

wr_cur_status <= wr_nxt_status;

end

always @(*) begin

if (a_reset_sync)

wr_nxt_status <= WR_IDLE;

else

case(wr_cur_status)

WR_IDLE : begin

if (s_axi_awvalid && s_axi_wvalid)

wr_nxt_status <= WE_DATA;

else

wr_nxt_status <= wr_cur_status;

end

WE_DATA : begin

wr_nxt_status <= WR_BRESP;

end

WR_BRESP : begin

if (s_axi_bvalid && s_axi_bready)

wr_nxt_status <= WR_IDLE;

else

wr_nxt_status <= wr_cur_status;

end

default : wr_nxt_status <= WR_IDLE;

endcase

end

always @(*) begin

if (a_reset_sync) begin

s_axi_awready <= 0;

s_axi_wready <= 0;

end

else begin

s_axi_awready <= wr_cur_status == WE_DATA;

s_axi_wready <= wr_cur_status == WE_DATA;

end

end

always @(posedge axi_clk) begin

if (a_reset_sync)

s_axi_bvalid <= 0;

else if (s_axi_bvalid && s_axi_bready)

s_axi_bvalid <= 0;

else if (wr_cur_status == WR_BRESP)

s_axi_bvalid <= 1'b1;

else

s_axi_bvalid <= s_axi_bvalid;

end

always @(posedge axi_clk) begin

if (wr_cur_status == WE_DATA) begin

s_wr_vld <= 1'b1;

s_wr_data <= s_axi_wdata;

s_wr_addr <= s_axi_awaddr;

end

else begin

s_wr_vld <= 0;

s_wr_data <= s_wr_data;

s_wr_addr <= s_wr_addr;

end

end

/*------------------------------------------*\

AXILITE从机读过程

\*------------------------------------------*/

always @(posedge axi_clk) begin

if (a_reset_sync)

rd_cur_status <= RD_IDLE;

else

rd_cur_status <= rd_nxt_status;

end

always @(*) begin

if (a_reset_sync)

rd_nxt_status <= RD_IDLE;

else

case(rd_cur_status)

RD_IDLE : begin

if (s_axi_arvalid)

rd_nxt_status <= RD_PRE;

else

rd_nxt_status <= rd_cur_status;

end

RD_PRE : begin

rd_nxt_status <= RD_DATA;

end

RD_DATA : begin

if (s_axi_rvalid && s_axi_rready)

rd_nxt_status <= RD_IDLE;

else

rd_nxt_status <= rd_cur_status;

end

default : rd_nxt_status <= RD_IDLE;

endcase

end

always @(*) begin

if (a_reset_sync)

s_axi_arready <= 0;

else

s_axi_arready <= rd_cur_status == RD_PRE;

end

always @(posedge axi_clk) begin

if (rd_cur_status == RD_PRE) begin

s_rd_addr_vld <= 1'b1;

s_rd_addr <= s_axi_araddr;

end

else begin

s_rd_addr_vld <= 0;

s_rd_addr <= s_rd_addr;

end

end

always @(posedge axi_clk) begin

if (a_reset_sync) begin

s_axi_rdata <= 0;

s_axi_rvalid <= 0;

end

else if (s_axi_rvalid && s_axi_rready) begin

s_axi_rvalid <= 0;

end

else if (s_rd_data_vld) begin

s_axi_rvalid <= 1'b1;

s_axi_rdata <= s_rd_data;

end

else begin

s_axi_rvalid <= s_axi_rvalid;

s_axi_rdata <= s_axi_rdata;

end

end

endmodule

user_ram:

`timescale 1ns / 1ps

module user_ram #(

parameter USER_WR_DATA_WIDTH = 32 ,

parameter USER_RD_DATA_WIDTH = 32 ,

parameter AXI_DATA_WIDTH = 32 , //注意AXI4的数据位宽只有32Bit或者64bit

parameter AXI_ADDR_WIDTH = 32

)(

input clk ,

input reset ,

input s_wr_vld ,

input [USER_WR_DATA_WIDTH-1:0] s_wr_data ,

input [AXI_ADDR_WIDTH-1 :0] s_wr_addr ,

input s_rd_addr_vld,

input [AXI_ADDR_WIDTH-1 :0] s_rd_addr ,

output reg [USER_RD_DATA_WIDTH-1:0] s_rd_data ,

output reg s_rd_data_vld

);

localparam SIZE = 1024;

reg [AXI_DATA_WIDTH-1:0] ram [SIZE - 1 : 0] ;

always @(posedge clk) begin

if (s_wr_vld)

ram[s_wr_addr] <= s_wr_data;

end

always @(posedge clk) begin

if (reset) begin

s_rd_data_vld <= 0;

s_rd_data <= 0;

end

else if (s_rd_addr_vld) begin

s_rd_data_vld <= 1'b1;

s_rd_data <= ram[s_rd_addr];

end

else begin

s_rd_data_vld <= 0;

s_rd_data <= 0;

end

end

endmodule

IP核生成

在ZYNQ开发中,要将构建的axi4lite_slave和user_ram打包为 IP核

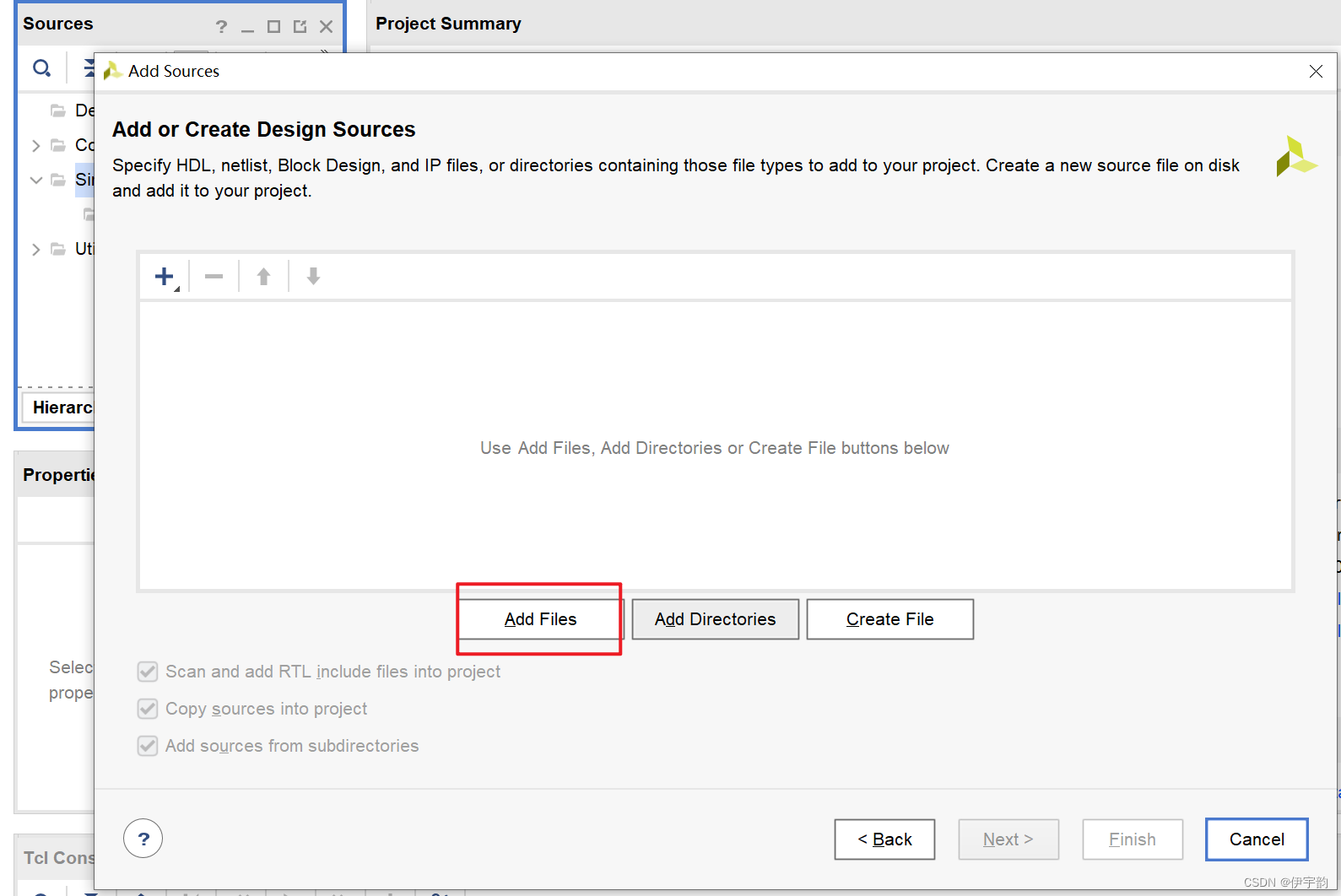

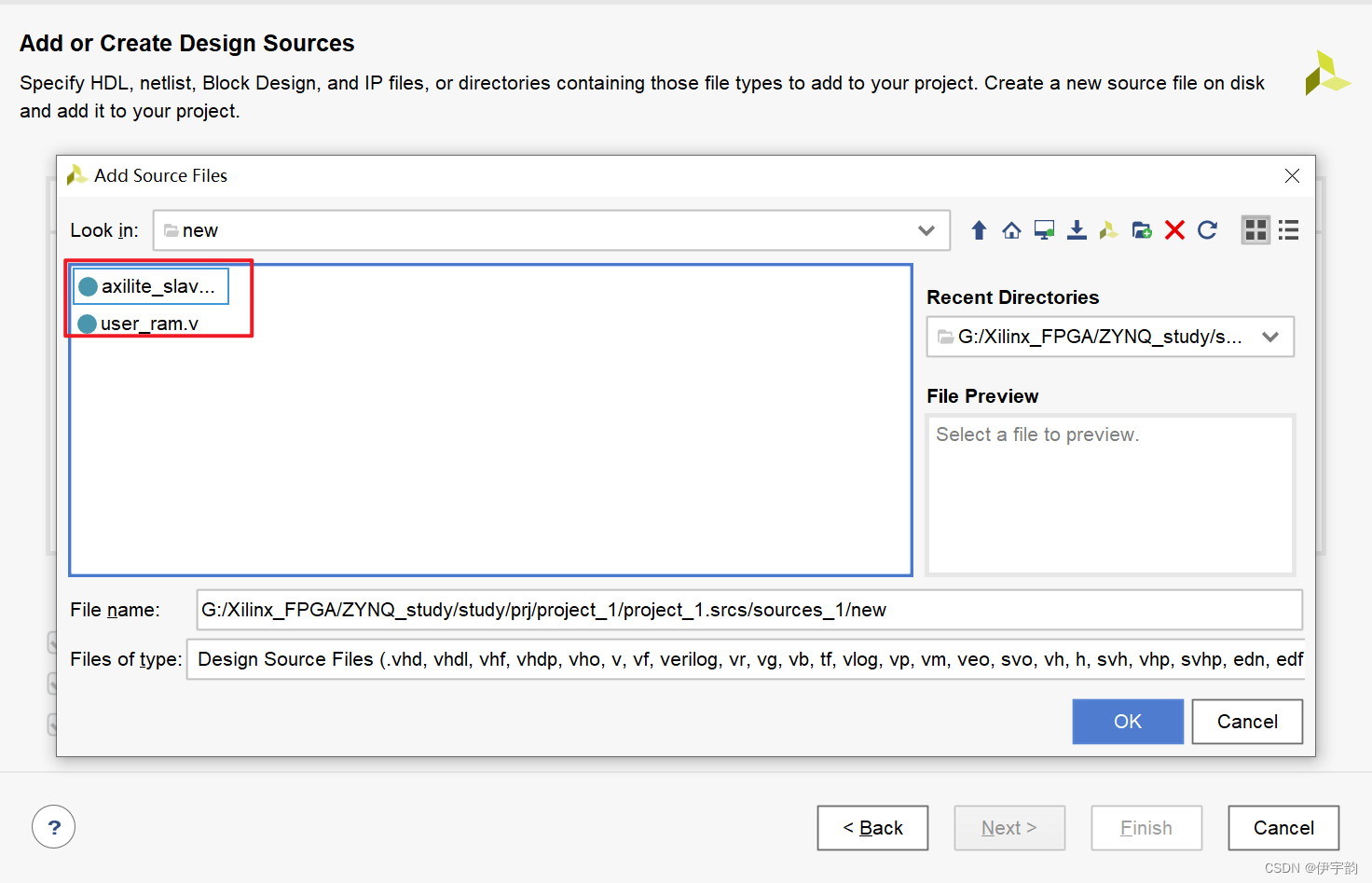

首先,创建新工程,将axi4lite_slave和user_ram代码导入:

点击OK

点击Finish

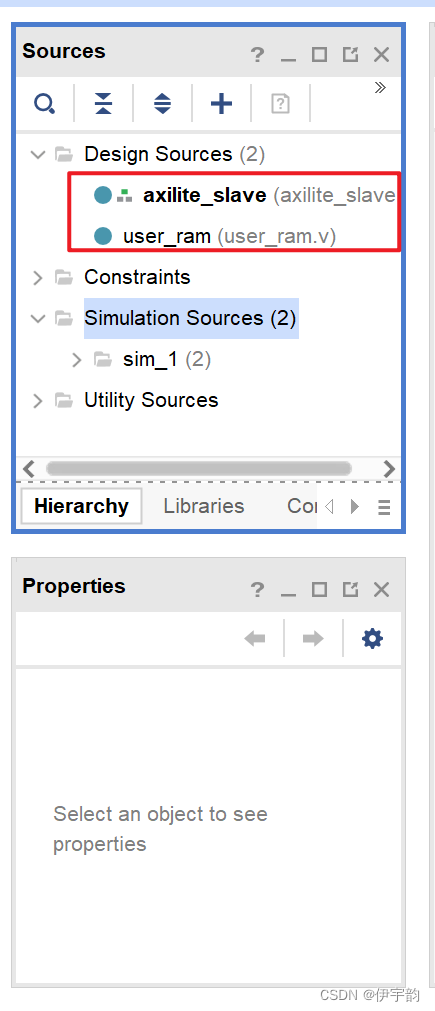

可以看到在Sources界面中已经有axi4lite_slave和user_ram文件

可以看到axi4lite_slave 是顶层。

---------------------------------------------------------------------------------------------------------------------------------

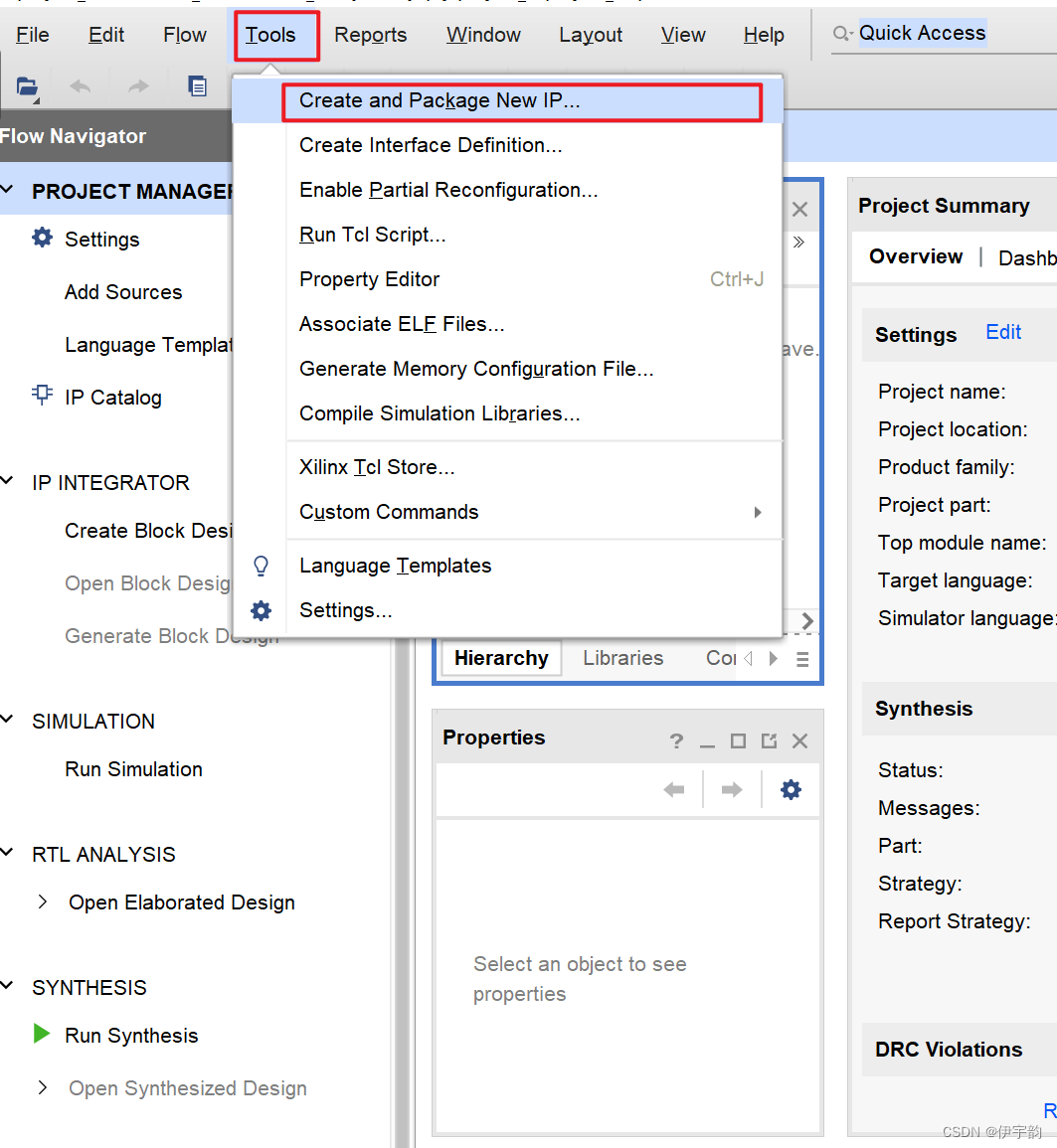

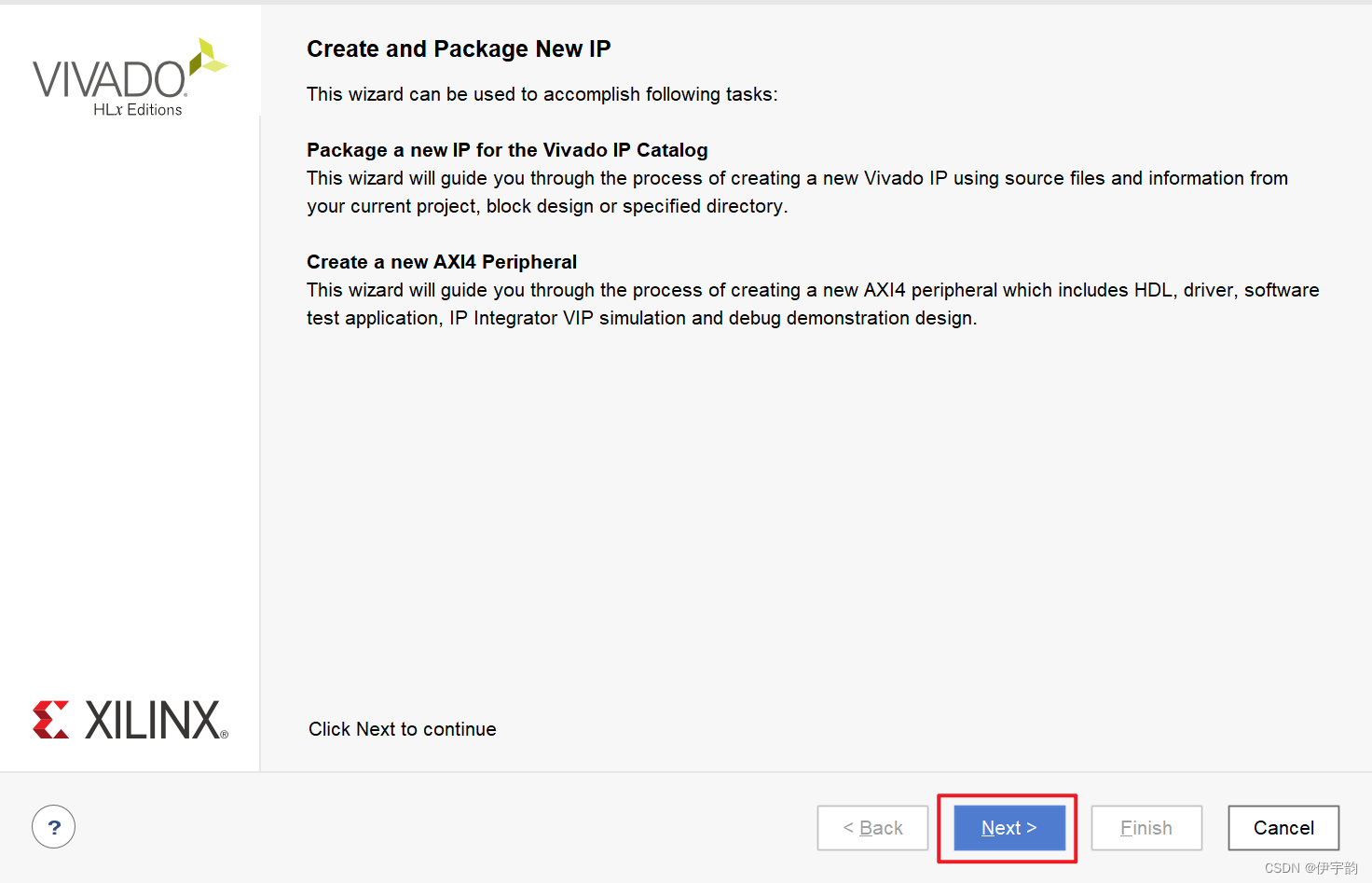

然后开始打包创建IP核

点击NEXT

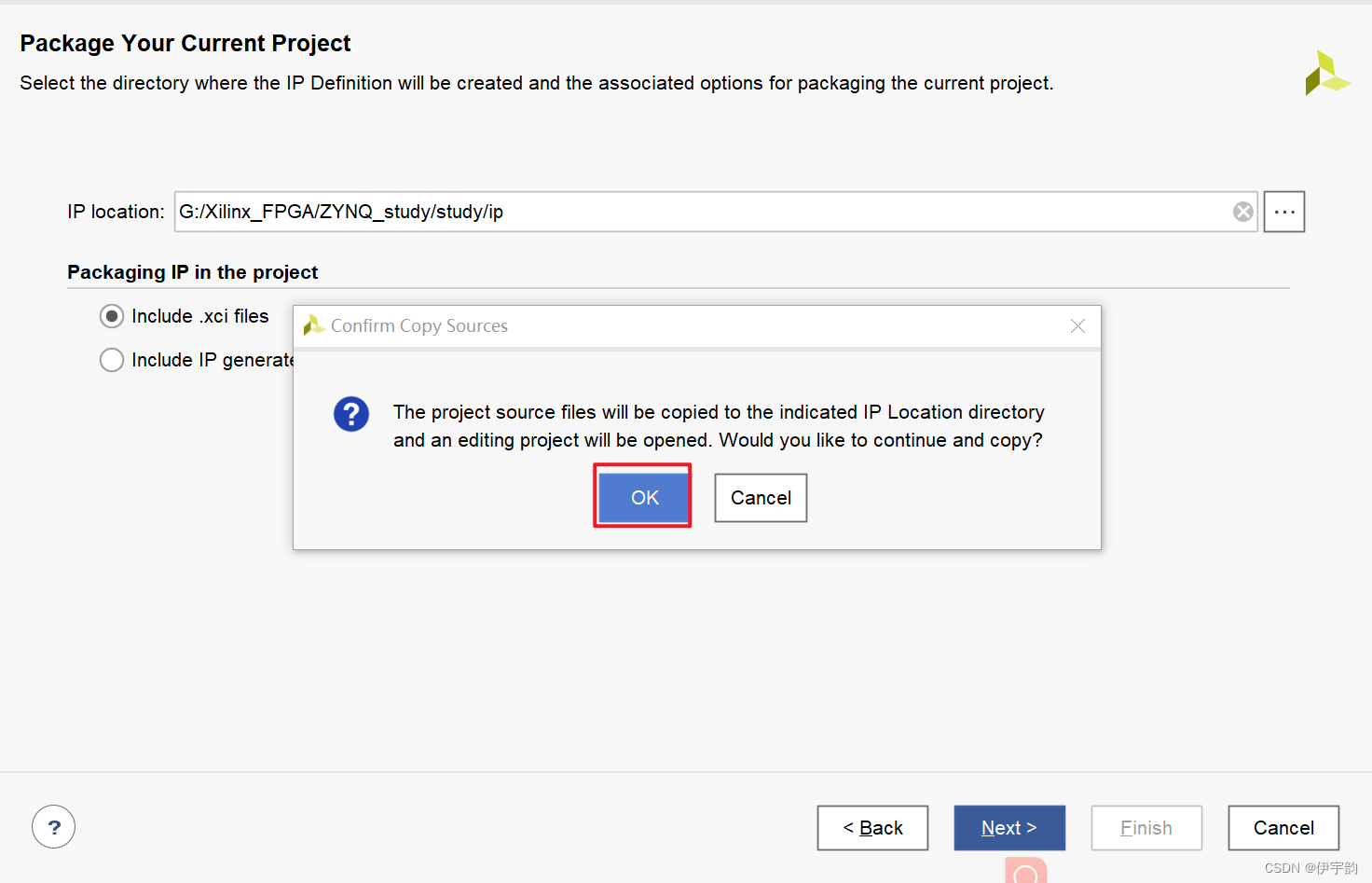

选择IP保存位置 点击Next

点击OK

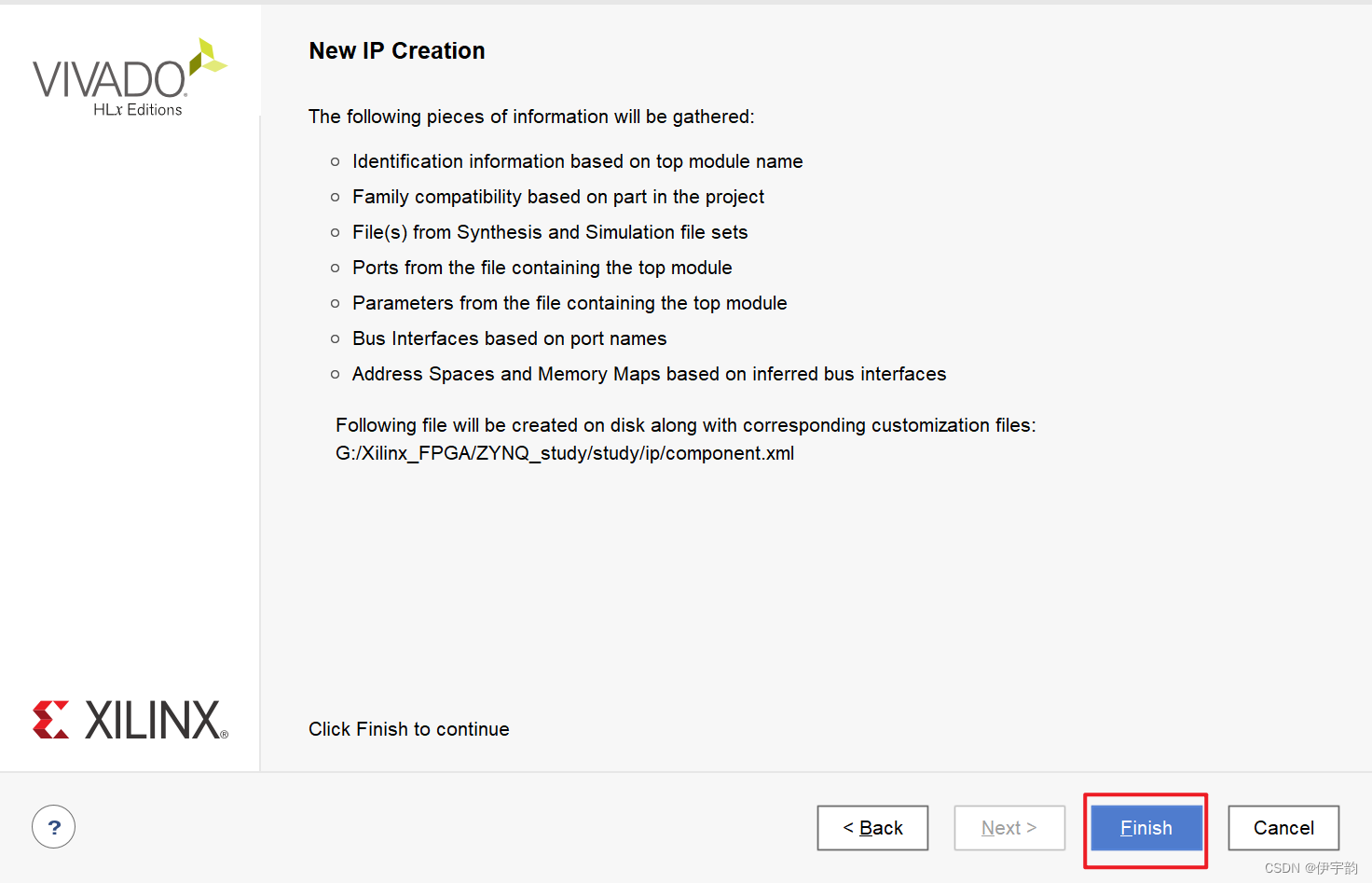

点击Finish

然后会弹出一个新工程:

这里是IP配置信息:

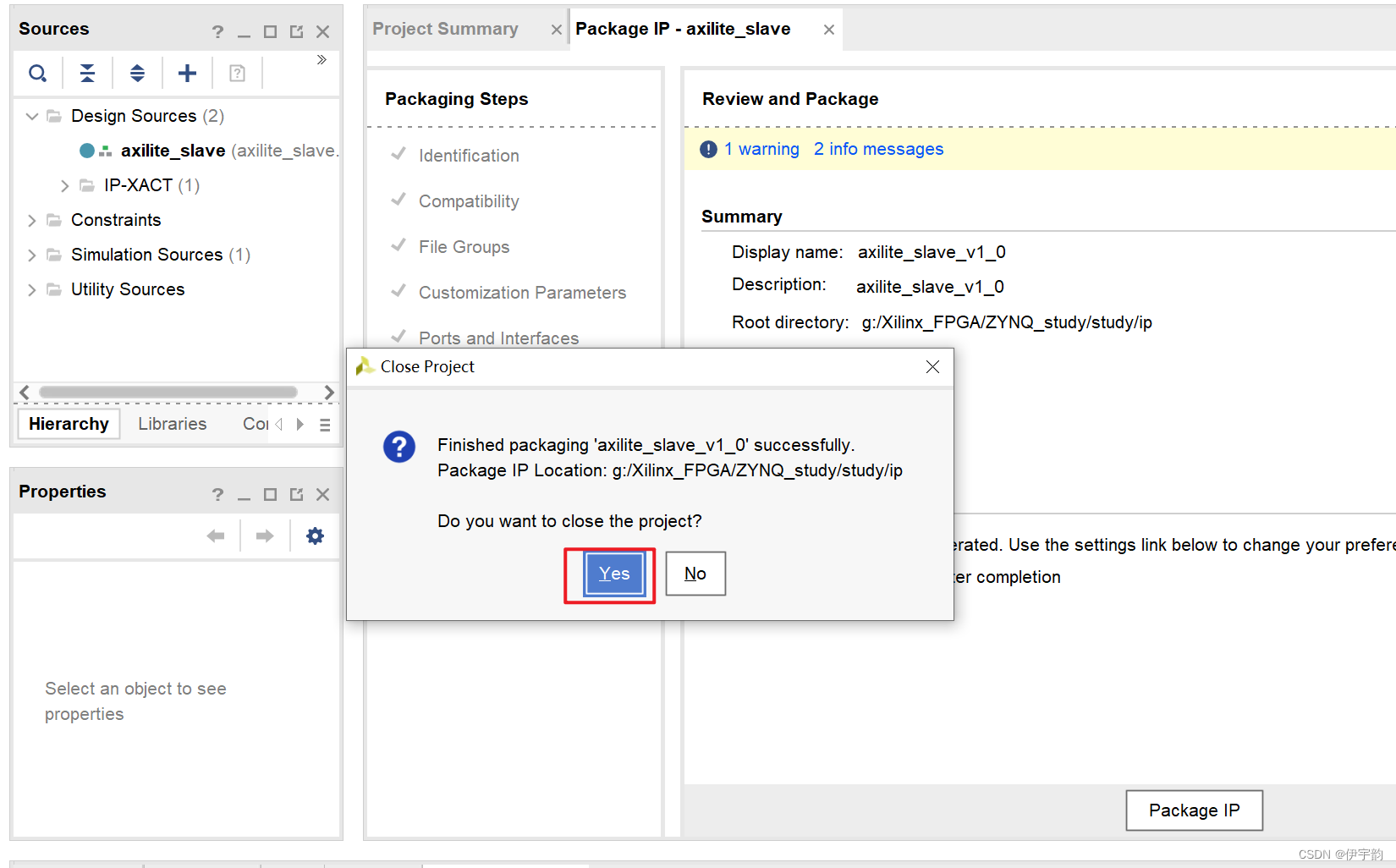

保持默认 然后点击Review and Package , 点击Package IP:

点击Yes

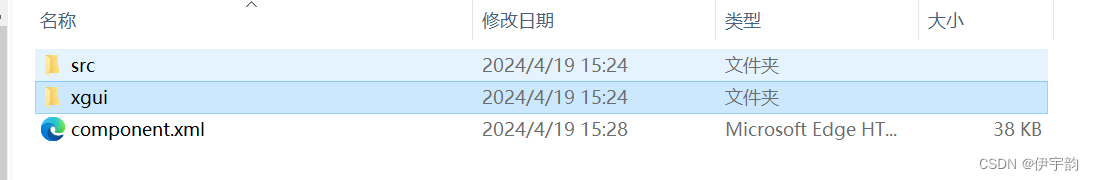

然后打开IP保存位置文件夹,可以看到如下:

点击src文件夹里面是axilite_slave.v文件

![]()

点击xgui文件夹是axilite_slave_v1_0.tcl文件![]()

这样axilite_slave IP核打包完成。

然后切换user_ram文件为顶层:

右击user_ram文件 点击Set as Top

然后重复axilite_slave打包过程,

打开IP核存放地址

至此,axi4lite_slave和user_ram文件打包ip核完成。

---------------------------------------------------------------------------------------------------------------------------------

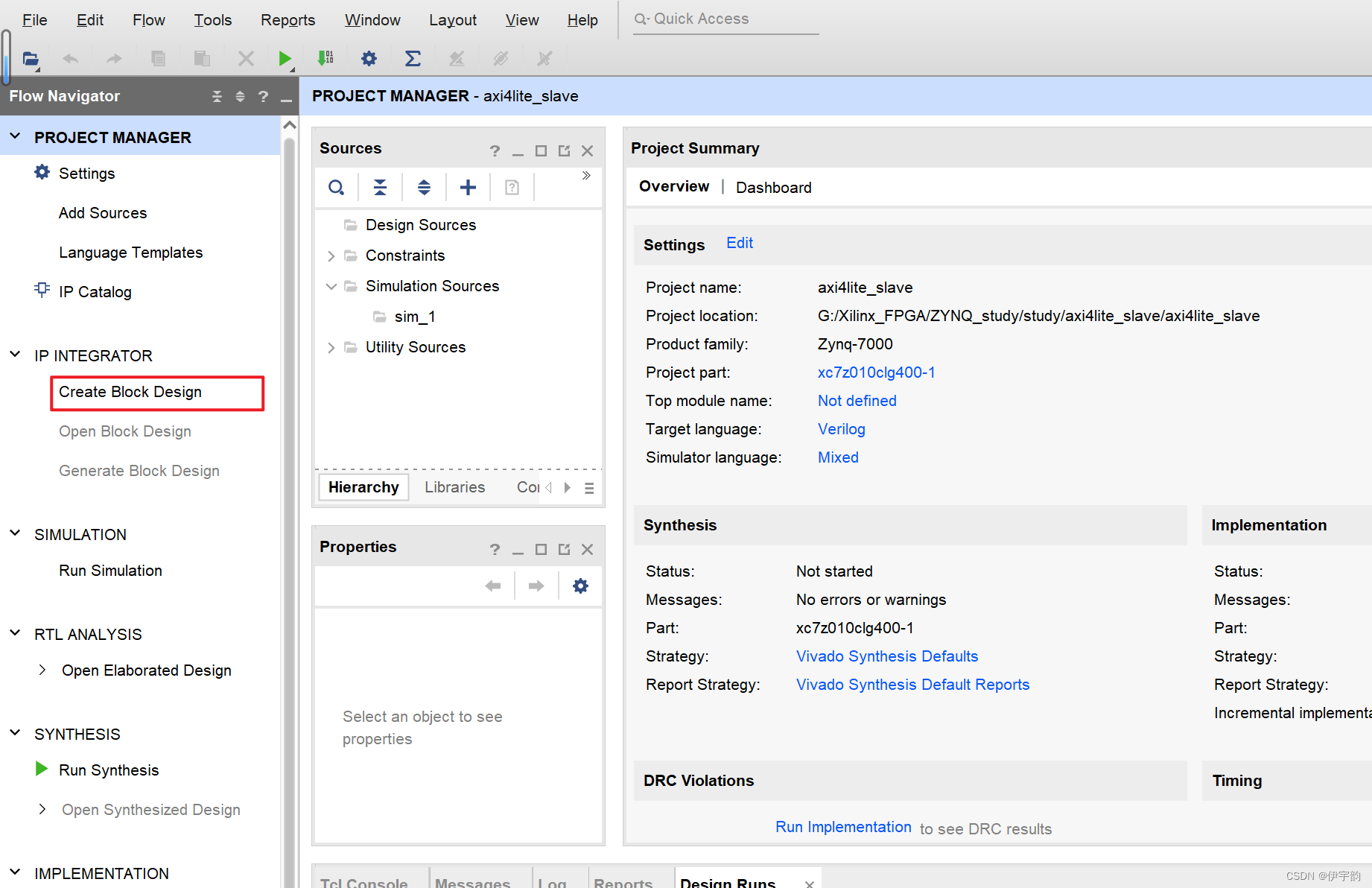

硬件系统搭建

搭建硬件系统

具体构建过程可见:

---------------------------------------------------------------------------------------------------------------------------------

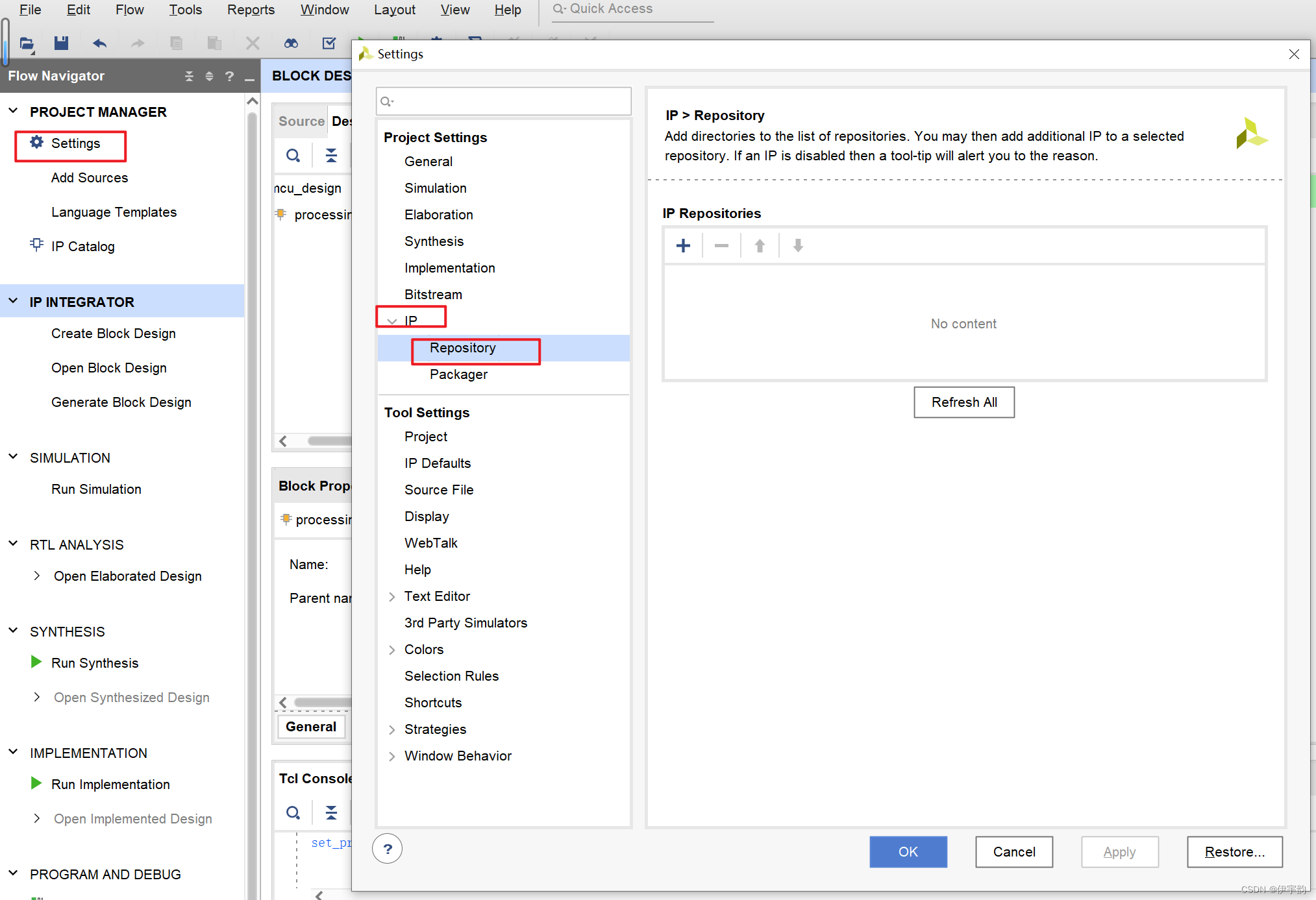

然后需要将上面打包的IP核,加载到IP库中:

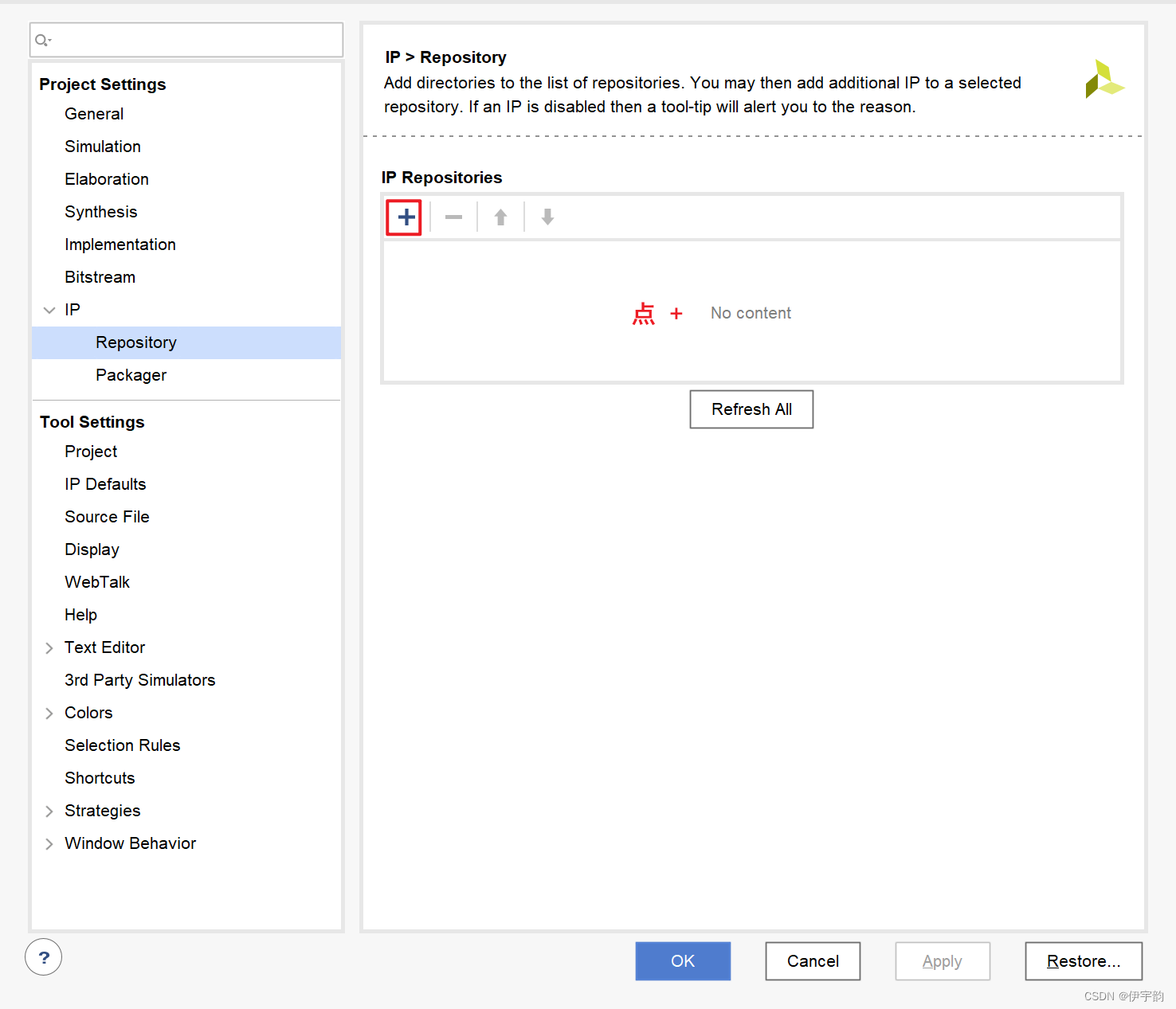

点击Seting ,再点击IP,然后点Repository

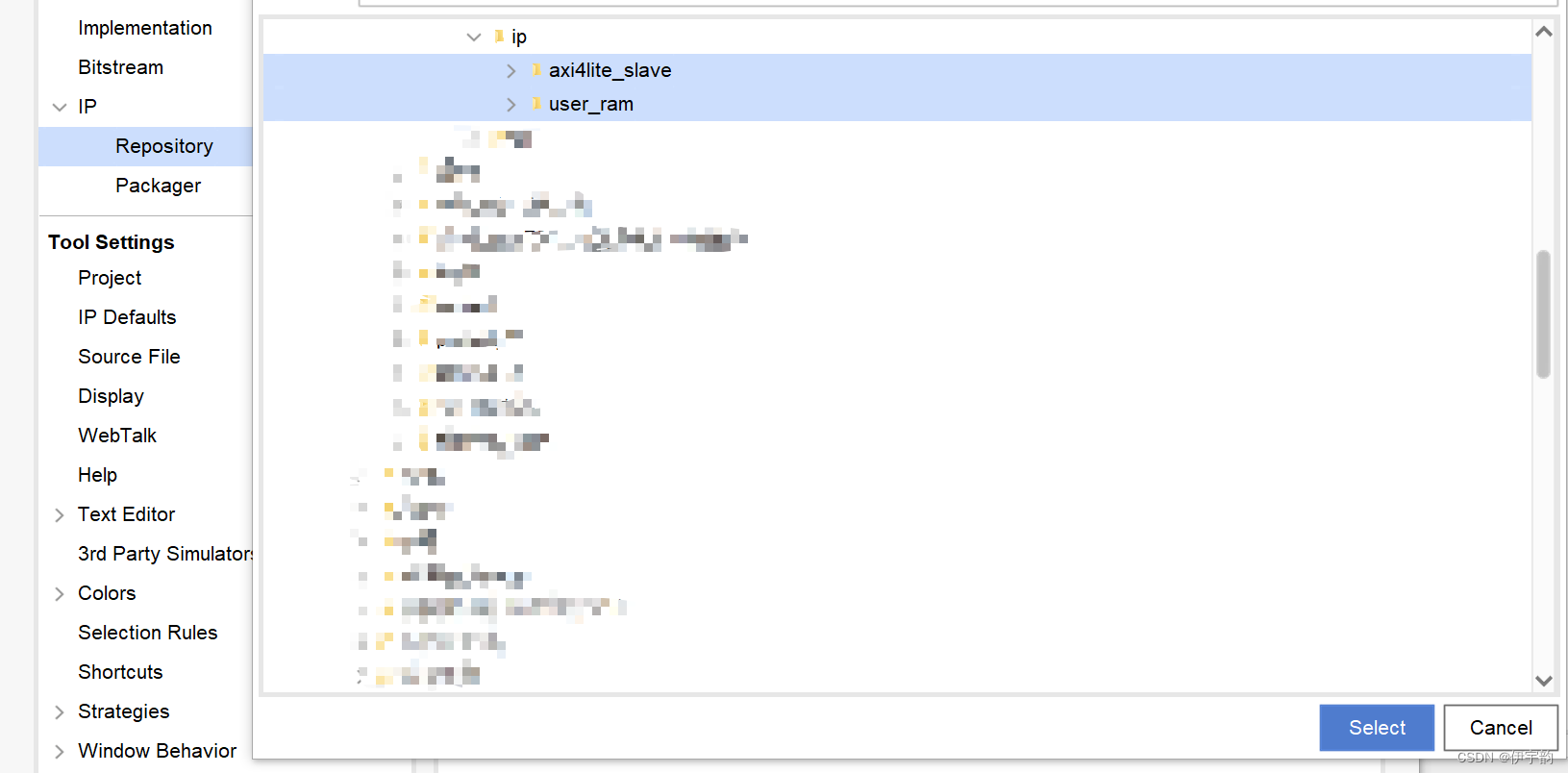

找到上面axi4lite_slave和user_ram IP 核存放位置,点击Select:

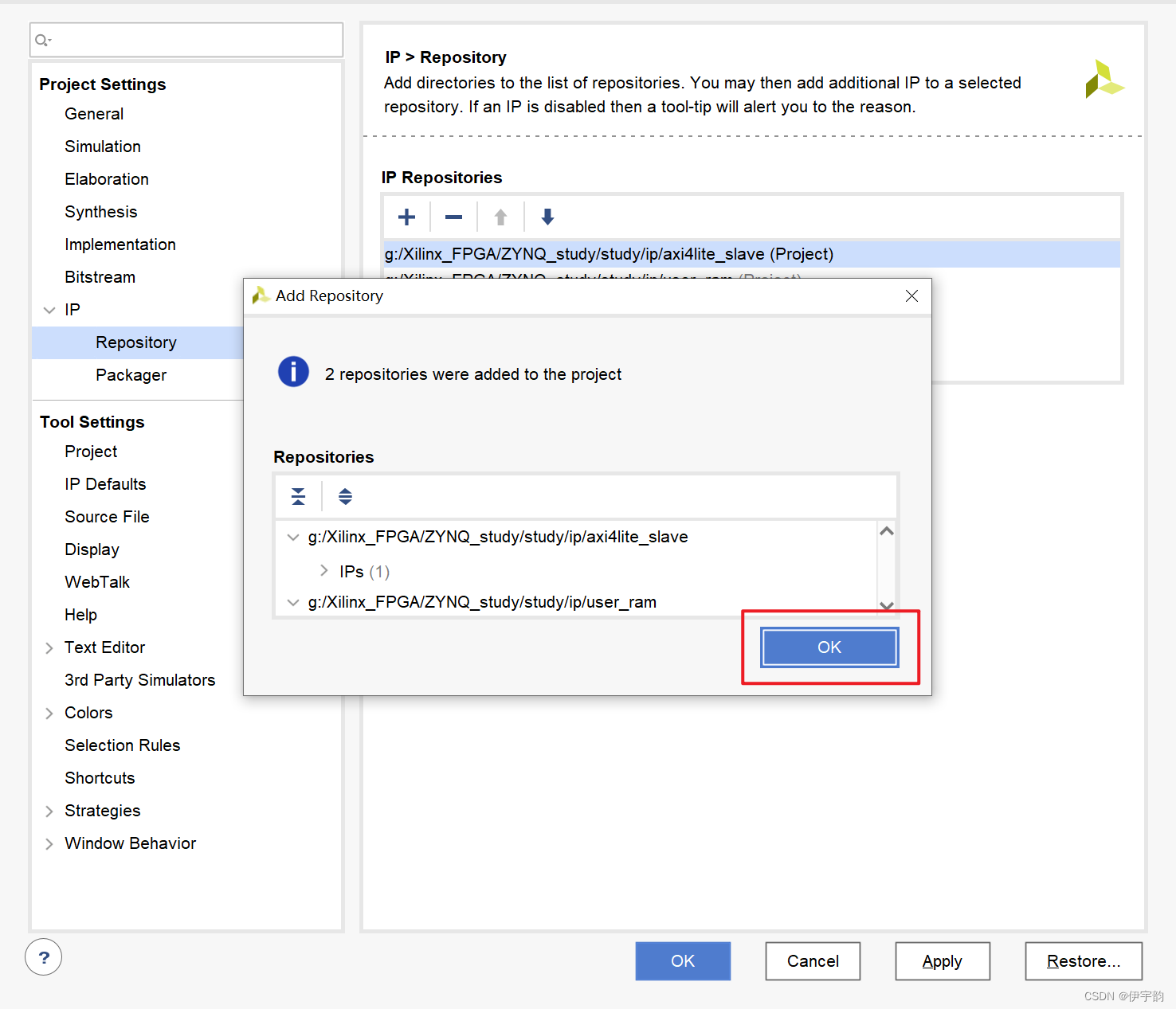

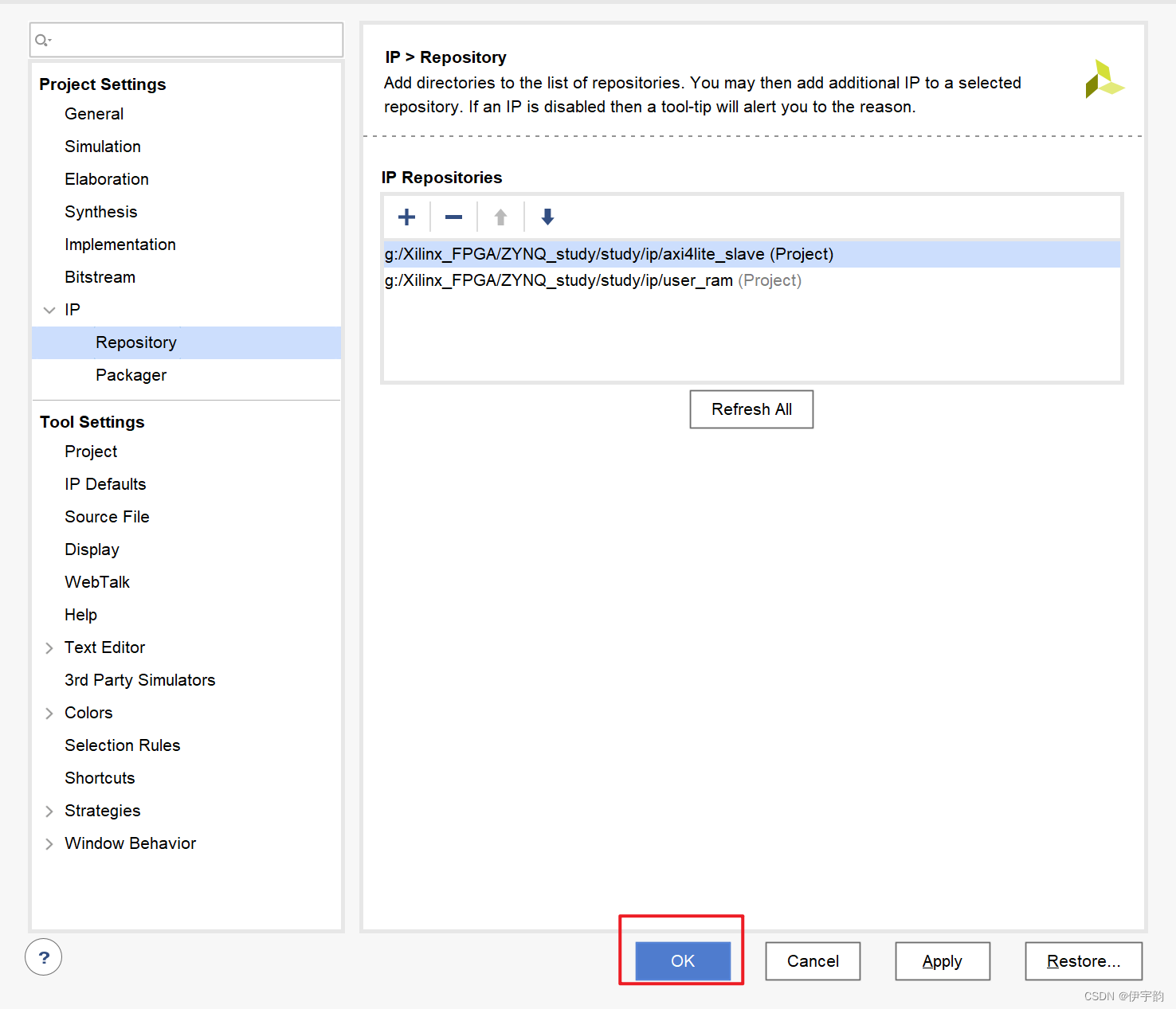

点击ok

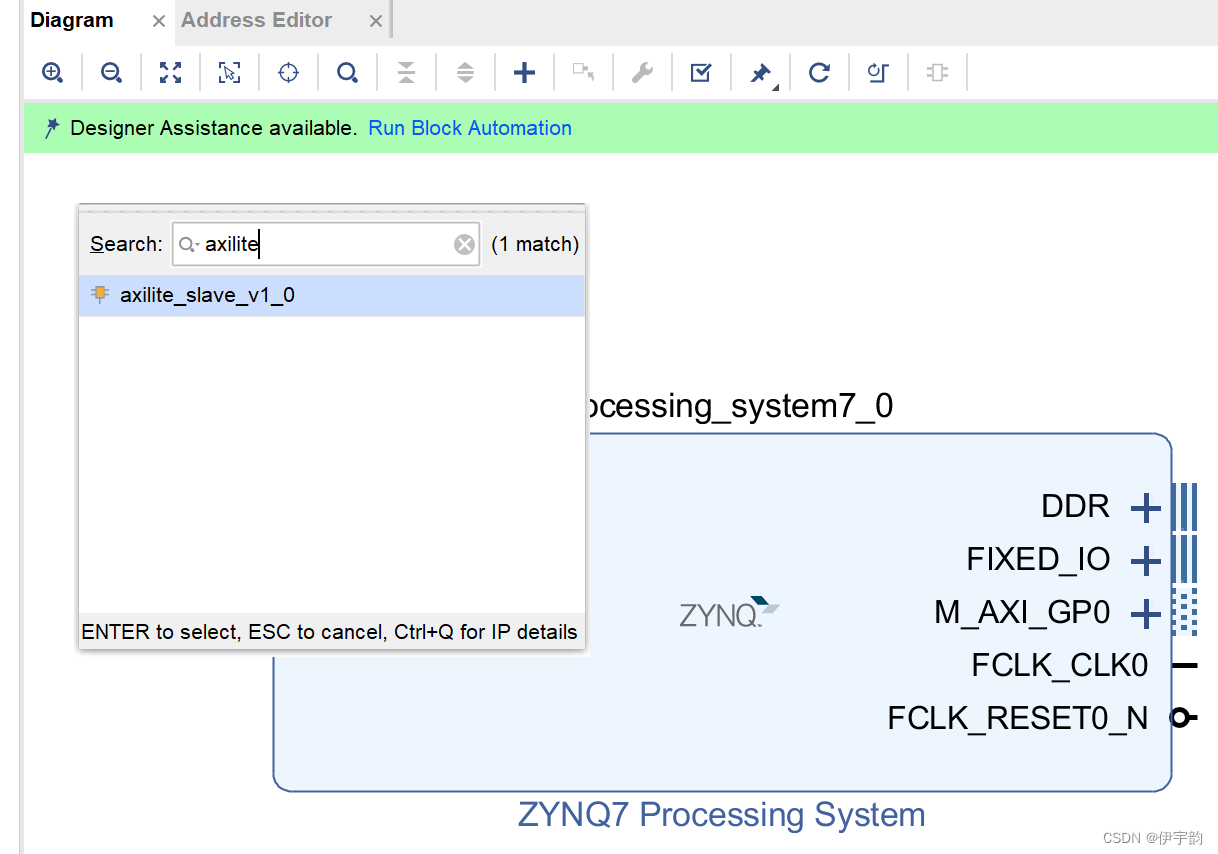

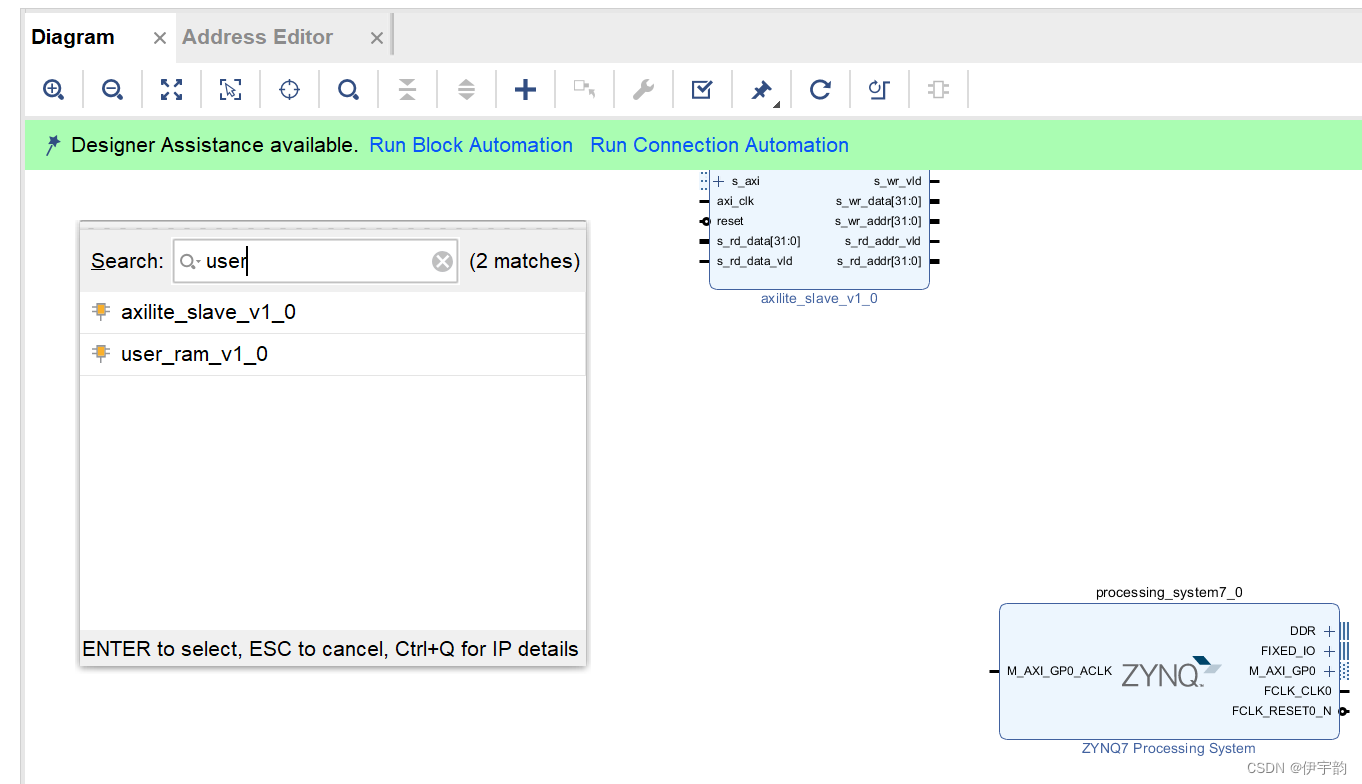

然后搜索axilite_slave和user_ram:

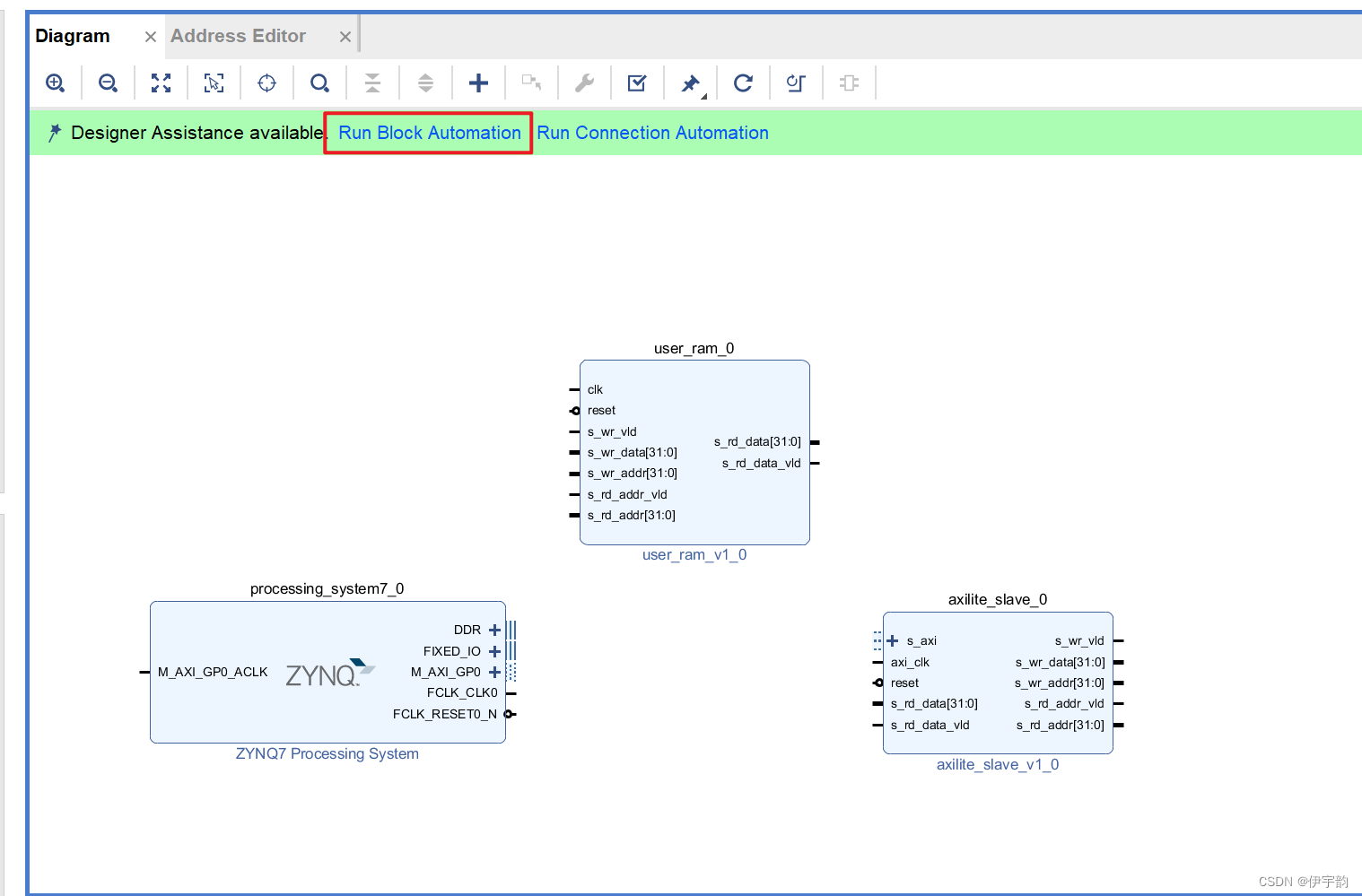

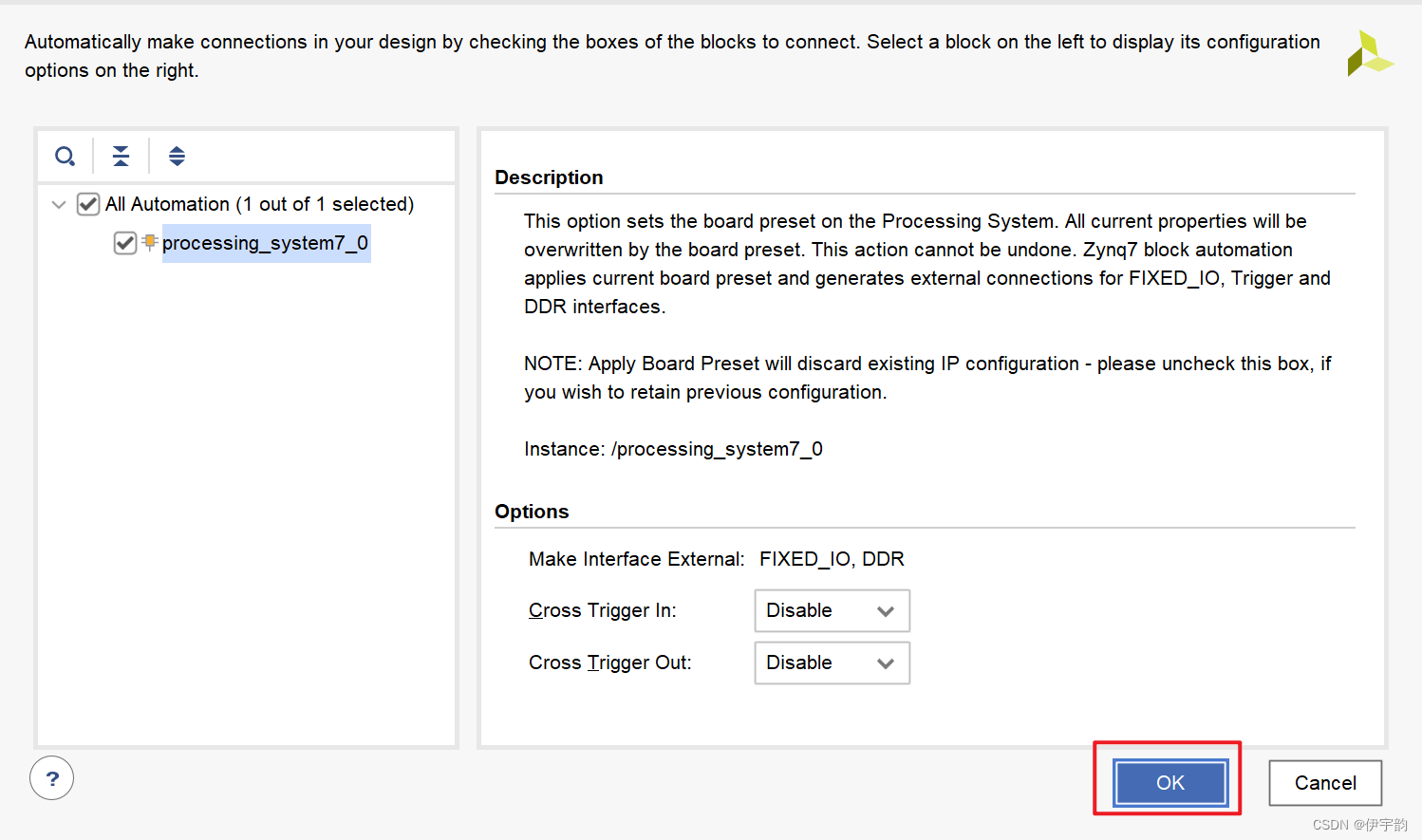

双击添加,点击Run Block Automation

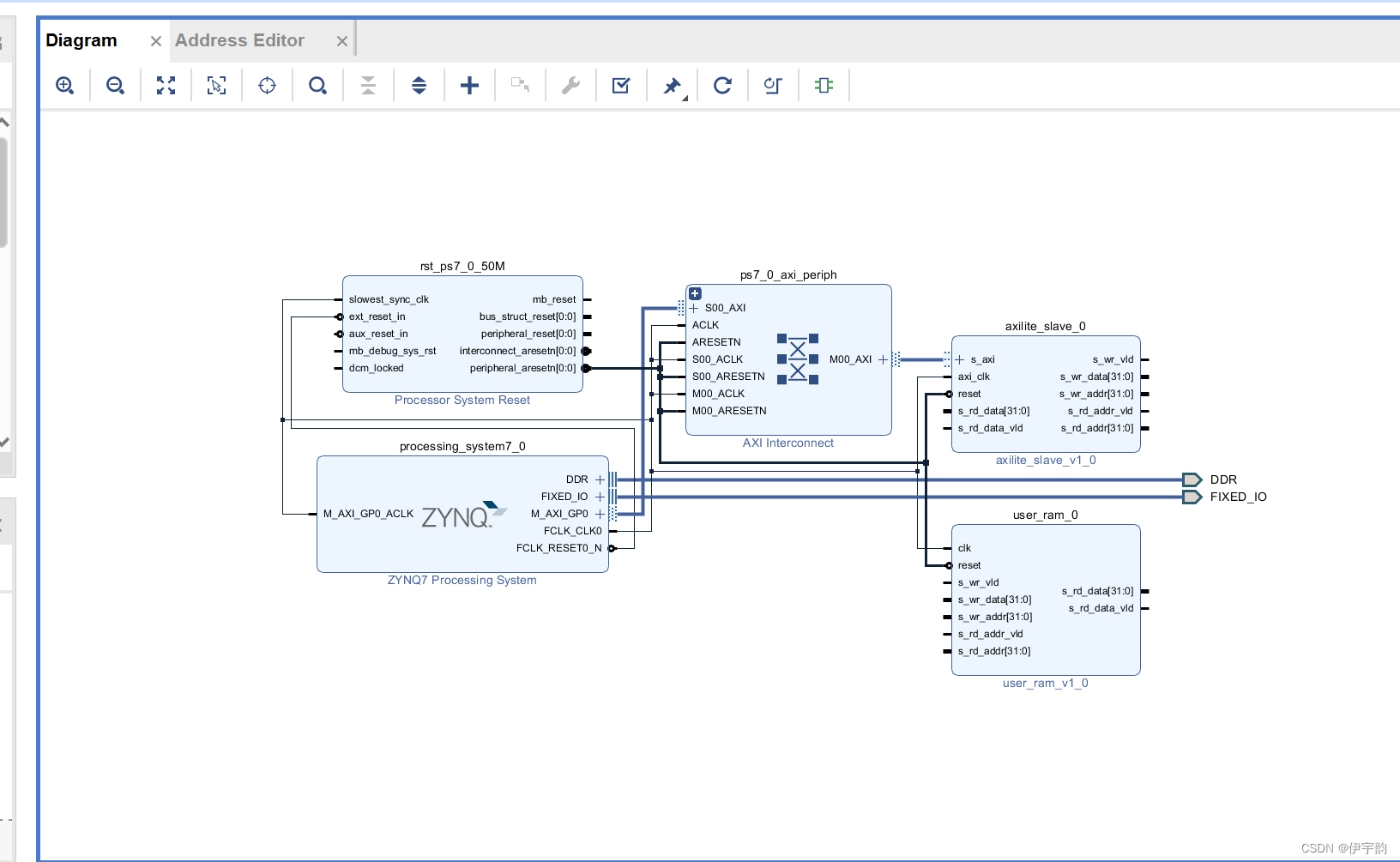

然后点击RUN connection Automation

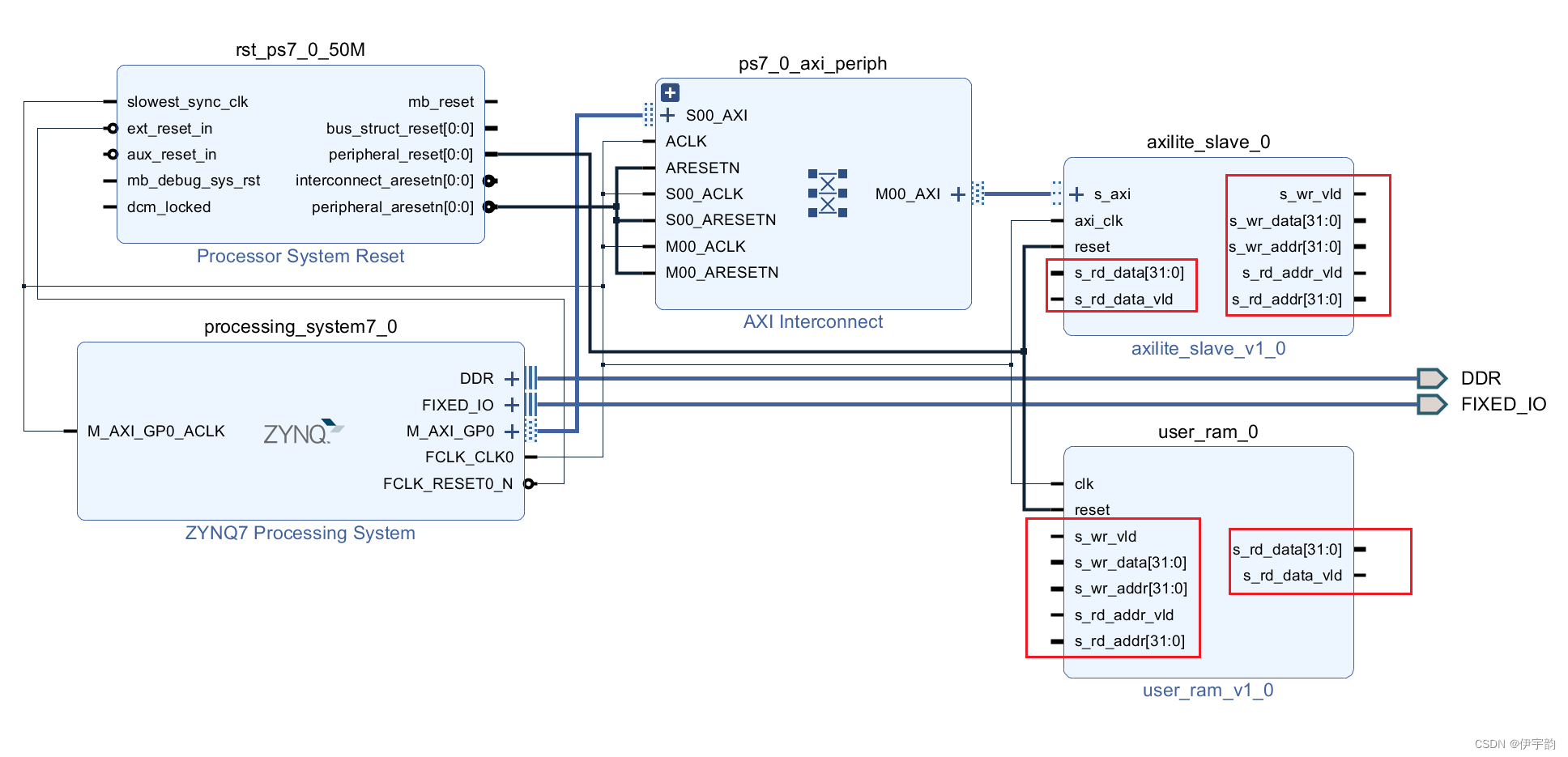

连线完成如下:

---------------------------------------------------------------------------------------------------------------------------------

由于axi4lite_slave和user_ram 是高复位,所以删除原来的低复位,重新连接高复位引脚:

删除重新连接:

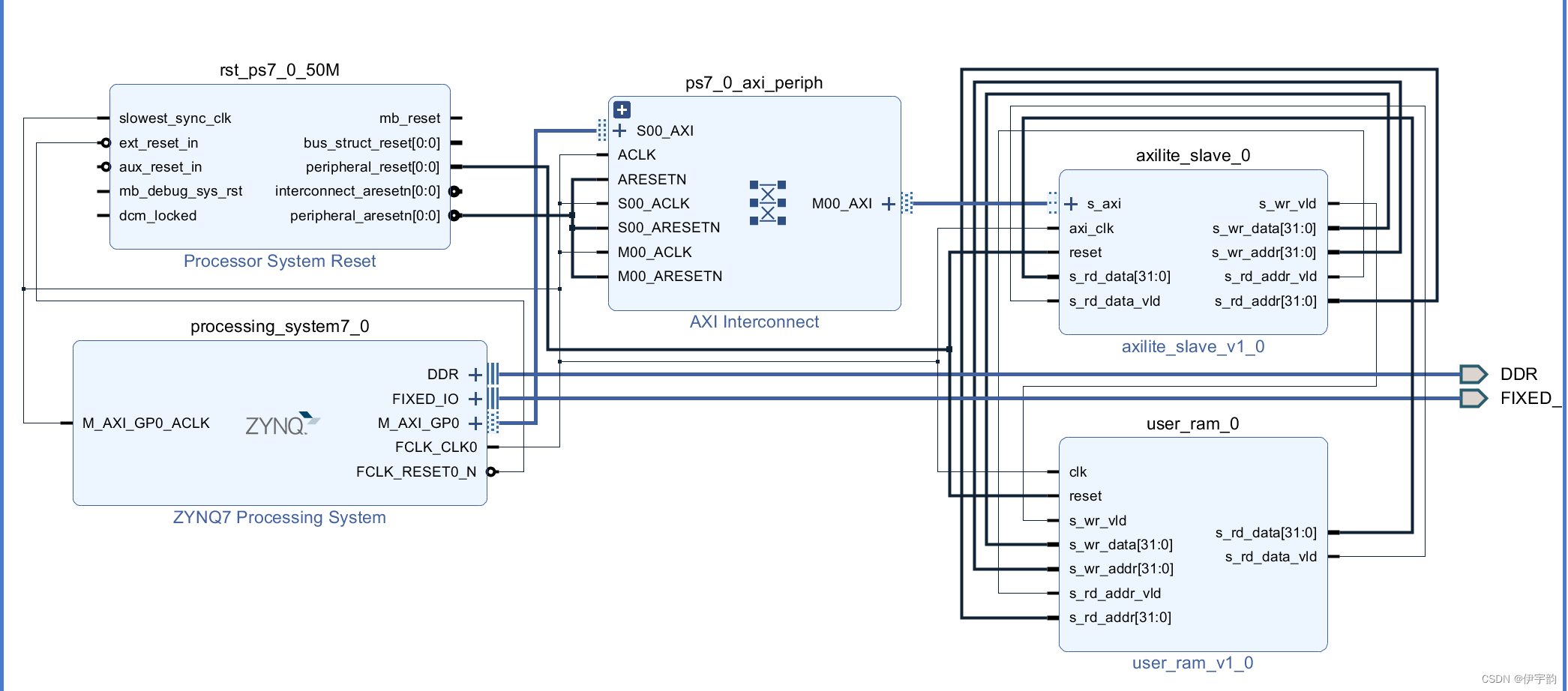

复位连接完成如下:

然后将axilite_slave 引脚 和user_ram 引脚相连:

连接完成如下:

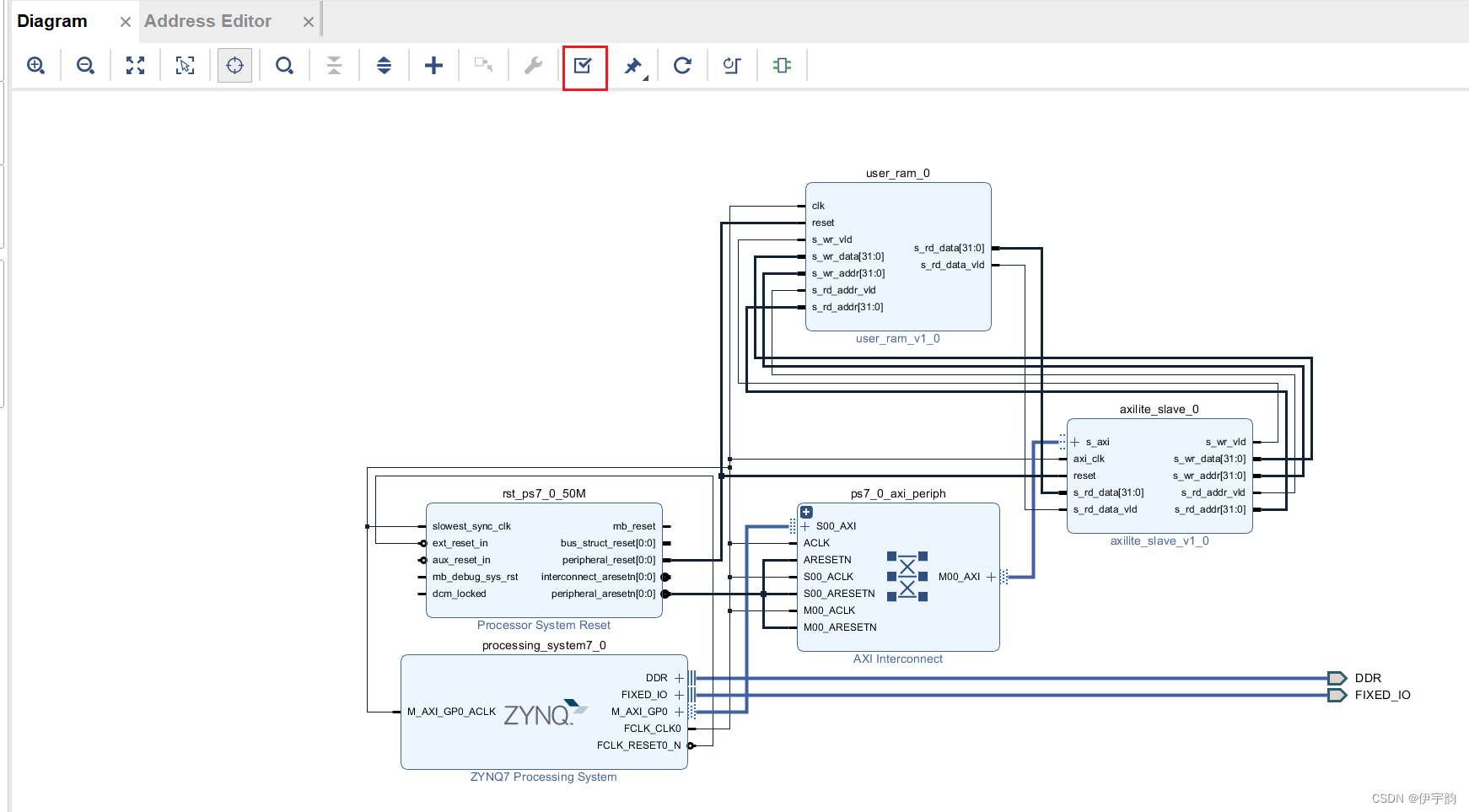

然后点击重新布局:

然后点击验证设计:

点击OK

然后按照FPGA - ZYNQ 基于EMIO的PS和PL交互中的开发流程:

生成封装,生成底层和顶层文件,

然后生成比特流,导出硬件,启动SDK。

---------------------------------------------------------------------------------------------------------------------------------

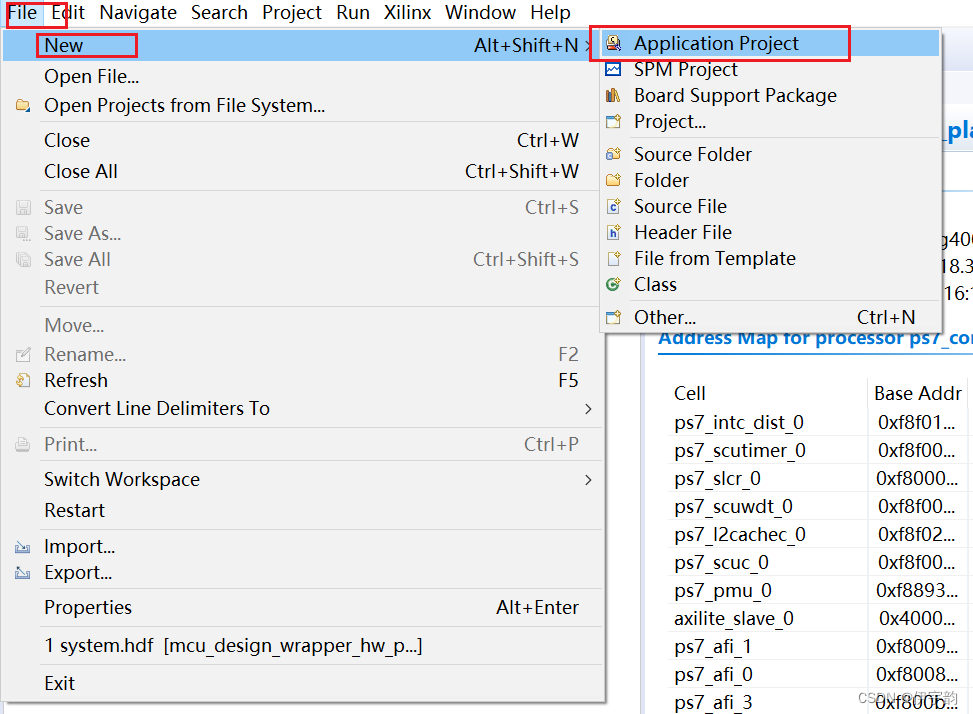

SDK 程序设计

创建SDK工程

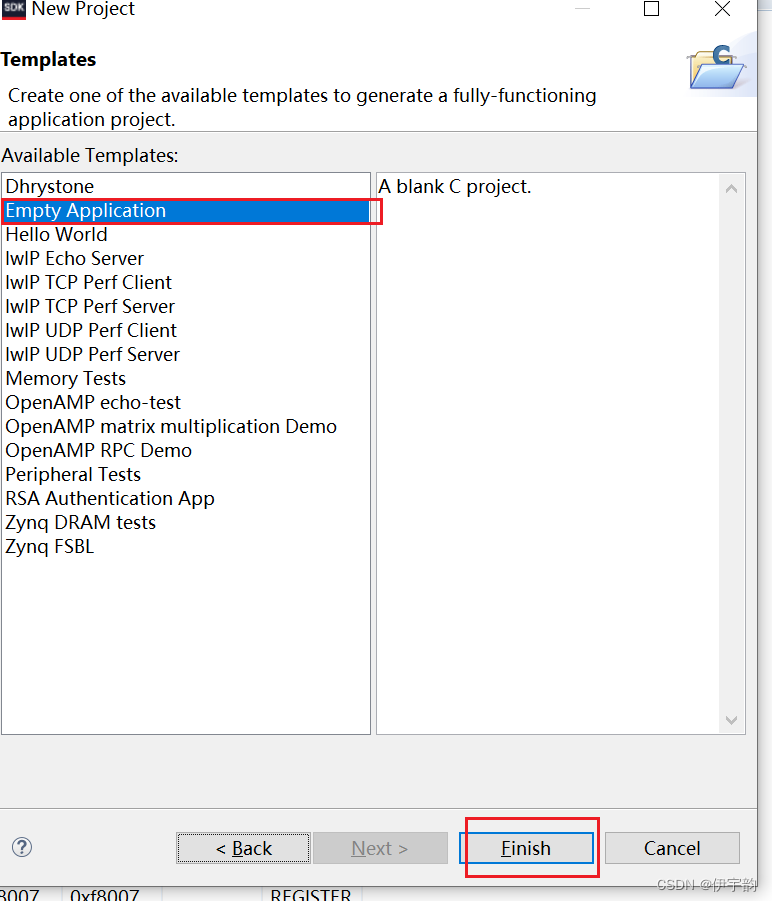

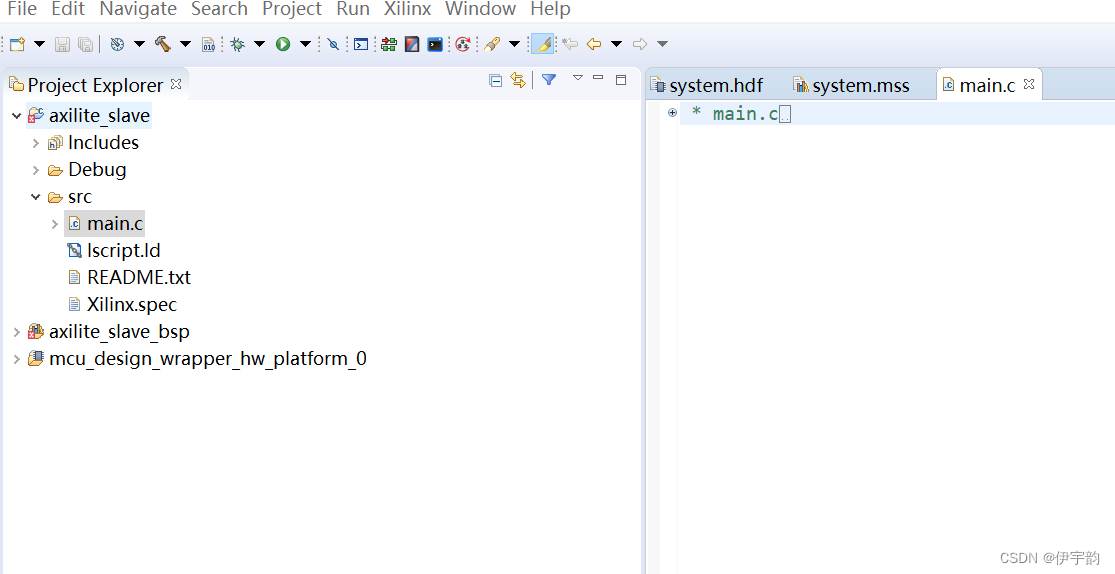

点击空工程 点击finish

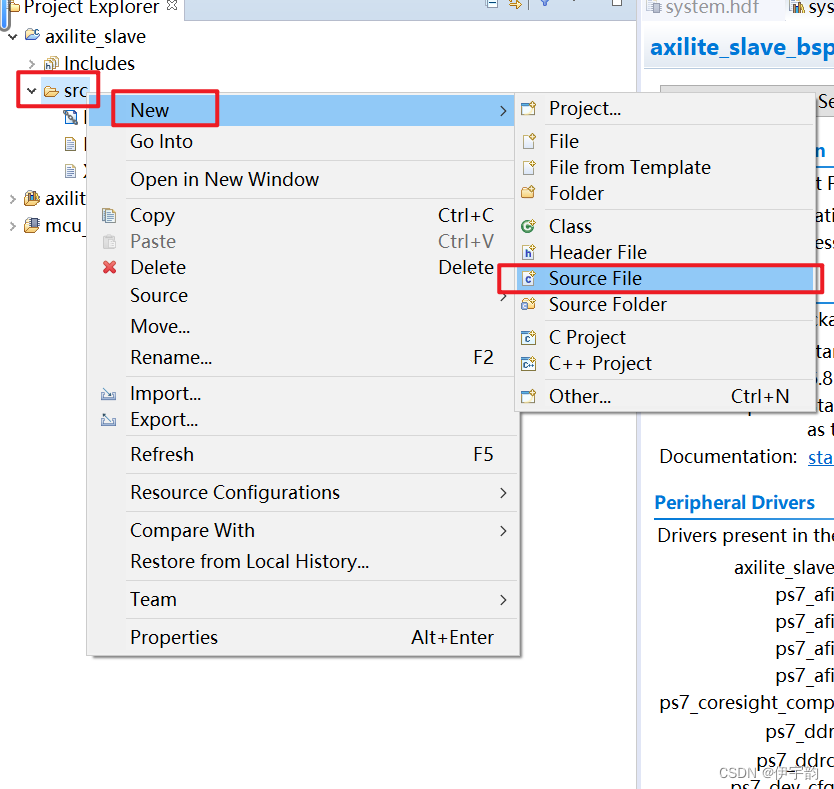

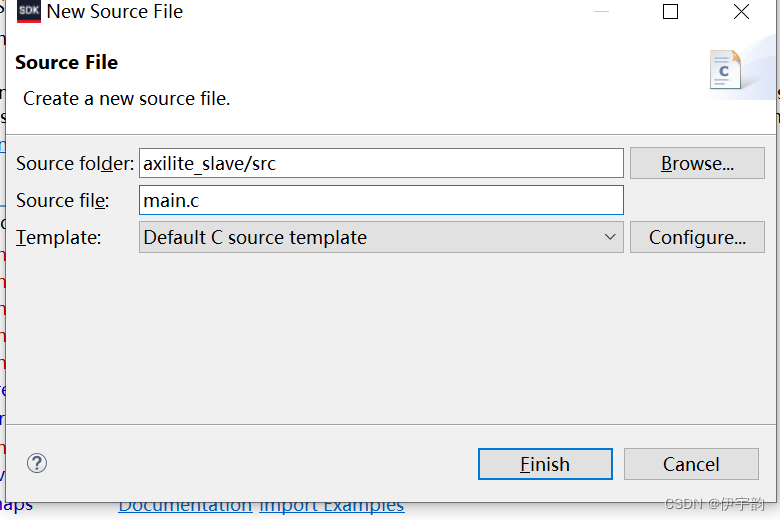

添加source file

---------------------------------------------------------------------------------------------------------------------------------

在硬件系统搭建中,我们看到,自动连线后,会出现一个AXI Interconnect。如下图:

这个模块在PS设计中,通过API接口实现axilite读写。

基于自定义AXI_lite 与 PS API接口 之间的映射关系

PS端API函数 和 AXI4_lite 总线的映射关系 对应关系

写入数据 Xil_Out32()函数

读出数据 Xil_In32() 函数

1,利用API接口函数实现读写axilite读写:

#include "xparameters.h"

#include "sleep.h"

#include "xil_io.h"

#define AXI_LITE_BASEADDR 0x40000000

通过函数编写

int main()

{

u32 rddata;

Xil_Out32(AXI_LITE_BASEADDR,1000);

Xil_Out32(AXI_LITE_BASEADDR + 4,500);

Xil_Out32(AXI_LITE_BASEADDR + 8,800);

rddata = Xil_In32(AXI_LITE_BASEADDR);

rddata = Xil_In32(AXI_LITE_BASEADDR + 4);

return 0;

}

2,利用指针实现读写axilite读写:

#include "xparameters.h"

#include "sleep.h"

#include "xil_io.h"

#define AXI_LITE_BASEADDR 0x40000000

int main()

{

u32* LitePtr = (u32*)AXI_LITE_BASEADDR; //强制转换 转为地址

u32 wrdata = 0;

u32 rddata = 0;

int i = 0;

//向PL写数据

for (i = 0; i < 128; i++ )

{

*LitePtr++ = wrdata++;

}

LitePtr = (u32*)AXI_LITE_BASEADDR;

for (i = 0; i < 128; i++ )

{

rddata = *LitePtr++;

printf("rddata= %d \n",rddata);

}

return 0;

}

最后,下载验证。

总结

在这里,实现了基于Axi_Lite的PS和PL交互,和axilite_slave(axilite从机)的实现,以及自定义IP核的创建,并且在SDK程序中实现了2种axilite的读写。

智能推荐

艾美捷Epigentek DNA样品的超声能量处理方案-程序员宅基地

文章浏览阅读15次。空化气泡的大小和相应的空化能量可以通过调整完全标度的振幅水平来操纵和数字控制。通过强调超声技术中的更高通量处理和防止样品污染,Epigentek EpiSonic超声仪可以轻松集成到现有的实验室工作流程中,并且特别适合与表观遗传学和下一代应用的兼容性。Epigentek的EpiSonic已成为一种有效的剪切设备,用于在染色质免疫沉淀技术中制备染色质样品,以及用于下一代测序平台的DNA文库制备。该装置的经济性及其多重样品的能力使其成为每个实验室拥有的经济高效的工具,而不仅仅是核心设施。

11、合宙Air模块Luat开发:通过http协议获取天气信息_合宙获取天气-程序员宅基地

文章浏览阅读4.2k次,点赞3次,收藏14次。目录点击这里查看所有博文 本系列博客,理论上适用于合宙的Air202、Air268、Air720x、Air720S以及最近发布的Air720U(我还没拿到样机,应该也能支持)。 先不管支不支持,如果你用的是合宙的模块,那都不妨一试,也许会有意外收获。 我使用的是Air720SL模块,如果在其他模块上不能用,那就是底层core固件暂时还没有支持,这里的代码是没有问题的。例程仅供参考!..._合宙获取天气

EasyMesh和802.11s对比-程序员宅基地

文章浏览阅读7.7k次,点赞2次,收藏41次。1 关于meshMesh的意思是网状物,以前读书的时候,在自动化领域有传感器自组网,zigbee、蓝牙等无线方式实现各个网络节点消息通信,通过各种算法,保证整个网络中所有节点信息能经过多跳最终传递到目的地,用于数据采集。十多年过去了,在无线路由器领域又把这个mesh概念翻炒了一下,各大品牌都推出了mesh路由器,大多数是3个为一组,实现在面积较大的住宅里,增强wifi覆盖范围,智能在多热点之间切换,提升上网体验。因为节点基本上在3个以内,所以mesh的算法不必太复杂,组网形式比较简单。各厂家都自定义了组_802.11s

线程的几种状态_线程状态-程序员宅基地

文章浏览阅读5.2k次,点赞8次,收藏21次。线程的几种状态_线程状态

stack的常见用法详解_stack函数用法-程序员宅基地

文章浏览阅读4.2w次,点赞124次,收藏688次。stack翻译为栈,是STL中实现的一个后进先出的容器。要使用 stack,应先添加头文件include<stack>,并在头文件下面加上“ using namespacestd;"1. stack的定义其定义的写法和其他STL容器相同, typename可以任意基本数据类型或容器:stack<typename> name;2. stack容器内元素的访问..._stack函数用法

2018.11.16javascript课上随笔(DOM)-程序员宅基地

文章浏览阅读71次。<li> <a href = "“#”>-</a></li><li>子节点:文本节点(回车),元素节点,文本节点。不同节点树: 节点(各种类型节点)childNodes:返回子节点的所有子节点的集合,包含任何类型、元素节点(元素类型节点):child。node.getAttribute(at...

随便推点

layui.extend的一点知识 第三方模块base 路径_layui extend-程序员宅基地

文章浏览阅读3.4k次。//config的设置是全局的layui.config({ base: '/res/js/' //假设这是你存放拓展模块的根目录}).extend({ //设定模块别名 mymod: 'mymod' //如果 mymod.js 是在根目录,也可以不用设定别名 ,mod1: 'admin/mod1' //相对于上述 base 目录的子目录}); //你也可以忽略 base 设定的根目录,直接在 extend 指定路径(主要:该功能为 layui 2.2.0 新增)layui.exten_layui extend

5G云计算:5G网络的分层思想_5g分层结构-程序员宅基地

文章浏览阅读3.2k次,点赞6次,收藏13次。分层思想分层思想分层思想-1分层思想-2分层思想-2OSI七层参考模型物理层和数据链路层物理层数据链路层网络层传输层会话层表示层应用层OSI七层模型的分层结构TCP/IP协议族的组成数据封装过程数据解封装过程PDU设备与层的对应关系各层通信分层思想分层思想-1在现实生活种,我们在喝牛奶时,未必了解他的生产过程,我们所接触的或许只是从超时购买牛奶。分层思想-2平时我们在网络时也未必知道数据的传输过程我们的所考虑的就是可以传就可以,不用管他时怎么传输的分层思想-2将复杂的流程分解为几个功能_5g分层结构

基于二值化图像转GCode的单向扫描实现-程序员宅基地

文章浏览阅读191次。在激光雕刻中,单向扫描(Unidirectional Scanning)是一种雕刻技术,其中激光头只在一个方向上移动,而不是来回移动。这种移动方式主要应用于通过激光逐行扫描图像表面的过程。具体而言,单向扫描的过程通常包括以下步骤:横向移动(X轴): 激光头沿X轴方向移动到图像的一侧。纵向移动(Y轴): 激光头沿Y轴方向开始逐行移动,刻蚀图像表面。这一过程是单向的,即在每一行上激光头只在一个方向上移动。返回横向移动: 一旦一行完成,激光头返回到图像的一侧,准备进行下一行的刻蚀。

算法随笔:强连通分量-程序员宅基地

文章浏览阅读577次。强连通:在有向图G中,如果两个点u和v是互相可达的,即从u出发可以到达v,从v出发也可以到达u,则成u和v是强连通的。强连通分量:如果一个有向图G不是强连通图,那么可以把它分成躲个子图,其中每个子图的内部是强连通的,而且这些子图已经扩展到最大,不能与子图外的任一点强连通,成这样的一个“极大连通”子图是G的一个强连通分量(SCC)。强连通分量的一些性质:(1)一个点必须有出度和入度,才会与其他点强连通。(2)把一个SCC从图中挖掉,不影响其他点的强连通性。_强连通分量

Django(2)|templates模板+静态资源目录static_django templates-程序员宅基地

文章浏览阅读3.9k次,点赞5次,收藏18次。在做web开发,要给用户提供一个页面,页面包括静态页面+数据,两者结合起来就是完整的可视化的页面,django的模板系统支持这种功能,首先需要写一个静态页面,然后通过python的模板语法将数据渲染上去。1.创建一个templates目录2.配置。_django templates

linux下的GPU测试软件,Ubuntu等Linux系统显卡性能测试软件 Unigine 3D-程序员宅基地

文章浏览阅读1.7k次。Ubuntu等Linux系统显卡性能测试软件 Unigine 3DUbuntu Intel显卡驱动安装,请参考:ATI和NVIDIA显卡请在软件和更新中的附加驱动中安装。 这里推荐: 运行后,F9就可评分,已测试显卡有K2000 2GB 900+分,GT330m 1GB 340+ 分,GT620 1GB 340+ 分,四代i5核显340+ 分,还有写博客的小盒子100+ 分。relaybot@re...