”CARRY4“ 的搜索结果

carry4 的构成

标签: fpga开发

利用Carry4进行高精度TDC设计,其MATLAB测试分析代码

理解在FPGA使用的加法减法,在FPGA底层中是如何实现,引出半加器、全加器概念,并理解FPGA中CARRY4的结构及功能

先说一段废话 近期萌生了写技术博客的念头,一来是可以记录一些遇到的技术问题,理清思路,也可以记录自己的技术成长;二来是可以将自己的知识分享,以便后人再碰到时能从容不破。希望今后在碰到原创有价值的问题时...

1.版本:matlab2014/2019a,内含运行结果,不会运行可私信 2.领域:智能优化算法、...4.适合人群:本科,硕士等教研学习使用 5.博客介绍:热爱科研的Matlab仿真开发者,修心和技术同步精进,matlab项目合作可si信

implementation of mser region detector

利用Carry4实现TDC

标签: fpga

Vivado工程,Carry4实现TDC,精度较高

对打印的部分模拟, 对打印的部分模拟

BMP图片锐化处理,补偿图像的轮廓,增强图像的边缘及灰度跳变的部分,使图像变得清晰,分为空域处理和频域处理两类。突出图像上地物的边缘、轮廓,或某些线性目标要素的特征。

基于FPGA的CARRY4 抽头延迟链 TDC延迟设计

欢迎使用Markdown编辑器写博客本...学习FPAG例程,发先综合后产生了一个CARRY4的逻辑单元。没看明白乍回事。决定研究一下。 查看官网说明: https://www.xilinx.com/support/documentation/user_guides/ug474_7Series

fpga中的进位链使用,加法器设计,行波进位加法器,超前进位加法器,CARRY4

16bit carry skip adder

进位链 carry 使用相关

标签: fpga开发

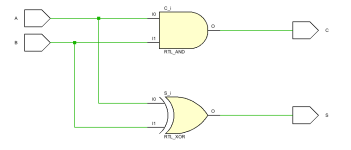

1、XILINX CARRY4 0、绪论 在聊进位逻辑之前,先准备一些预备知识关于加法器(半加器和全加器)电路; 0.1、半加器 半加器(half adder)的功能是将两个一位二进制数相加。它具有两个输入和两个输出,两个...

在FPGA中我们写的最多的逻辑是什么?... 可能很多刚开始接触FPGA的同学没听过进位链,也就是Carry Chain,我们这里再回顾一下。FPGA的三个主要资源为: 可编程逻辑单元 可配置逻辑单元(Configurable ...

采用FPGA的CARRY4进位单元,每个CARRY4的COUT连接到下一个CARRY4的CIN,这样级联起来,形成延时链;每个COUT做为抽头输出到触发器,通过本地时钟进行数据采样。假定每个延时链的延时是固定的(最后需要标定),可...

经典的进位跳跃、进位选择、并行前缀加法器,16位,基于verilog HDL语言

四位串行进位加法器在STEP MAX10开发板(10M02SCM153)上的VHDL实现使用Quartus Prime 20.1编写

搬运堆垛机已重新装载现在由维护

新视野大学英语第四册-unit6A-The-weight-men-carry.doc

8-bit carry select adder

Its a carry select adder which uses binary excess code in it for the reduction of delay.

CARRY SAVE ADDITION WITH EXAMPLE EXPLANATION

ripple carry adder vhdl code

进位存储乘法器Verilog代码,该乘法器的显著特点是其性能取决于使用的硬件而与数据长度无关.

推荐文章

- YOLOv7如何提高目标检测的速度和精度,基于优化算法提高目标检测速度-程序员宅基地

- linux中进程退出函数:exit()和_exit()的区别_linux结束进程可以用哪些函数,它们之间有何区别?-程序员宅基地

- sqlserver55555_sqlserver把小数点后面多余的0去掉-程序员宅基地

- Angular6 和 RXJS6 的一些改动_angular6,requestoptions改成了什么-程序员宅基地

- C++解析XML文件_c++ xml解析-程序员宅基地

- R语言使用caret包的train函数构建多元自适应回归样条(MARS)模型构建分类模型、trainControl函数设置交叉验证参数、自定义调优评估指标_多元自适应回归样条 r-程序员宅基地

- Android ListView控件显示数据库中图片_安卓获取listview里的图片并显示-程序员宅基地

- python123程序改错题库,2016最新二级C语言考试题库及答案(程序改错专项练习 精华版)...-程序员宅基地

- Roser S.Pressman在UMLChina交流实录-程序员宅基地

- 【Linux】shell编程1(shell脚本书写格式、脚本中的环境变量、普通变量、自定义环境变量、变量数组、位置变量、状态变量、内置变量、变量扩展)_linux脚本格式-程序员宅基地