FPGA通信第二篇--UDP

”FPGA底层结构“ 的搜索结果

第2节 FPGA芯片结构 1.2.1 FPGA工作原理与简介 如前所述,FPGA是在PAL、GAL、EPLD、CPLD等可编程器件的基础上进一步发展的产物。它是作为ASIC领域中的一种半定制电路而出现的,即解决了定制电路的不足,又克服...

FPGA 正是一种硬件可重构的体系结构。它的英文全称是Field ProgRammable GateArray,中文名是现场可编程门阵列。 PS:处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分。SOC(System On Chip) PL:可...

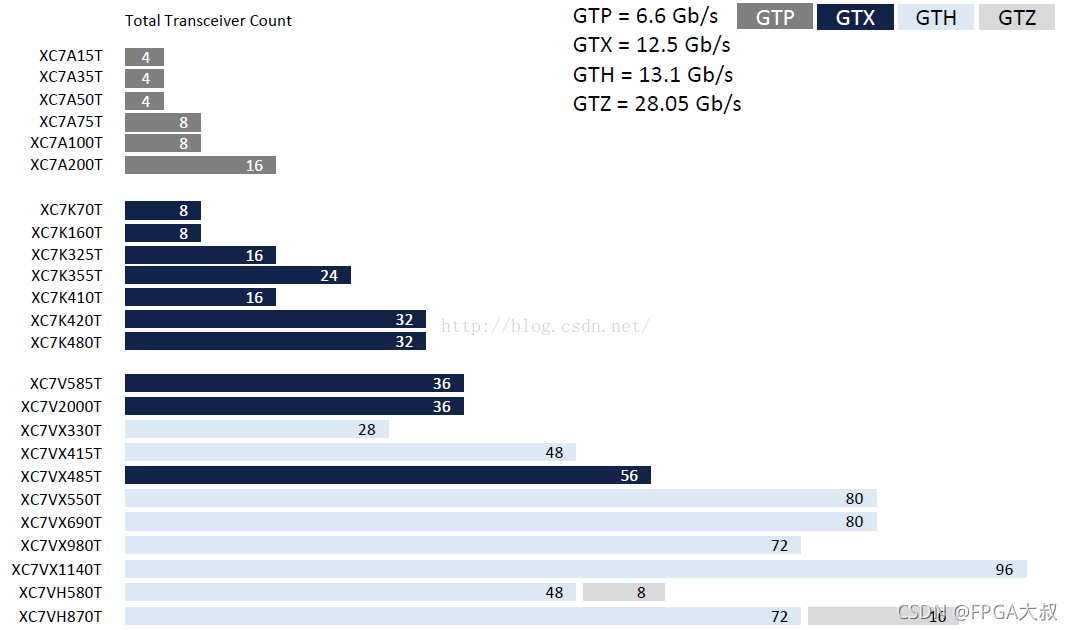

FPGA实现NIC 10G UDP协议栈网卡,纯verilog代码编写,提供工程源码和技术支持 本设计是一个10G速率的网卡,Xilinx Virtex-7 xc7vx690t调用Virtex-7 FPGA Gen3 Integrated Block for PCI Express IP核实现FPGA网卡与...

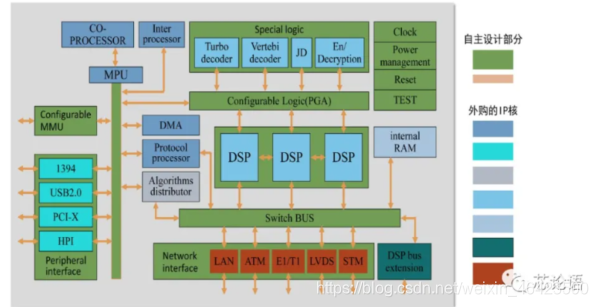

SOC是一个复杂的系统,它将一个完整产品的功能集成在一个芯片上,包括...Planahead 允许高层设计者为不同的模块划分相应FPGA芯片区域,并允许底层设计者在在所给定的区域内独立地进行设计、实现和优化,等各个模块...

LabVIEW FPGA PCIe开发讲解-7.2节:目前主流的4大Xilinx FPGA PCIe DMA通信IP核讲解(Xilinx官方XAPP1052和XMDA IP、以色列Xillybus多通道DMA IP、国外RIFFA IP、北大EPEE IP)-结论是Xillybus简单易用更方便!...

设计用户程序的编程语言,作为人类自然语言与底层芯片编程语言之间的桥梁,能够提供任务调度与管理、内存管理、任务间同步与通信、时间管理和中断服务等功能,振,但是精度没有外部配置的高速晶振精度高。...

虽然在一个小团队里面,一般都不会深入这个底层来实现具体的TLP包,要么是Riffa,要么是XDMA。但是架不住面试的时候有人会问啊,这就很恼火了啊。那怎么办,还不是只有来看看基础。其实Github上还真是有人实现过如此...

来源:内容来自财通证券TMT组,谢谢。 2018年上半年对于中国半导体行业而言是多事之秋,发生了几件让国人深入思考的大事。我作为IC产业的逃兵,最近也在思考很多的问题,包括资本市场、集成电路行业和研究所的一些...

嵌入式系统与桌面PC结构非常不同,但其底层技术发展却是一样的,而且遵循着类似发展趋势。当桌面PC转向64位架构来满足不断增长的存储器要求时,嵌入式系统也由于同样的原因快速转向32位处理器。桌面/服务器计算市场...

FPGA的图像处理开发及流程介绍

为什么很多人会觉得FPGA难学?

标签: 大数据

FPGA开发全攻略连载之七:底层内嵌功能单元与软核、硬核以及固核 1. 可编程输入输出单元(IOB) 可编程输入/ 输出单元简称I/O 单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/ 输出信号的驱动与...

RAM中也有一些参数,也有一些延迟,需要注意!因为有时它的特性并非如我们想象的那样,正确的流程应该是先看数据手册,再使用,但是对于很多设计者来说,总感觉这玩意太简单,但越是这样可能越会用错,不注意延迟,...

本文主要设计完成了改进中值滤波图像处理系统的硬件设计及算法设计,经过电路设计、设计输入、RTL仿真、综合优化、布局布线、时序仿真与验证、板级仿真与验证,以及芯片编程与调试,最后将码流加载到FPGA上。...

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.可编程输入/输出单元(I/O单元...

复杂是因为复位本身是对大规模的硬件单元进行一种操作,必须要结核底层的设计来考虑问题。1. 常见问题自己在学习实践过程中,以及看到网友询问的,有关FPGA复位设计大概有以下几类问题:我板子上没有设...

文章目录前言一、什么叫FPGA二、什么叫数字IC三、FPGA设计流程1.系统规划2.RTL输入3. 行为仿真/功能仿真4. 逻辑综合5. 综合后仿真(可选)6. 综合后设计分析(时序及资源)7. 设计实现(包括布局布线及优化)8. 布线后仿真...

以将工程分割为若干独立的子任务,在不需要大的改动情况下非常容易添加新的功能,成本、功耗和体积等要求限制,如此多因素的影响带来了差异性的设计,以至于很难。随着互联网的迅速发展,万物联网的时代已经快到了,...

图1-1只是一个示意图,实际上每一个系列的FPGA都有其相应的内部结构),FPGA芯片主 要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能...

这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数。 面积和速度这两个指标贯穿FPGA/CPLD设计的时钟,...

推荐文章

- linux shell脚本字符串连接符,学习Linux shell脚本中连接字符串的方法-程序员宅基地

- excel或wps查找文本字符串子串或拆分字符串公式_wps+excel+字符串取子串-程序员宅基地

- 阿里云ESC-Ubuntu图形化界面安装(解决安装后依然只有控制台的问题)_阿里云ecs服务器ubantu只有命令行-程序员宅基地

- 零基础制作服务器,问下大佬们 零基础学搭建服务器要学些啥-程序员宅基地

- ROSTCM6情感分析结果乱码_rostcm6情感分析error-程序员宅基地

- ubuntu实用指令_ubuntu命令大全-程序员宅基地

- 原生 table 浏览器 border 粗细不一致(谷歌90版本以后) table兼容问题_兼容模式下 table表格边框变粗的问题-程序员宅基地

- C调用汇编_c 里面调用汇编-程序员宅基地

- python求鸡兔同笼 鸡兔总数鸡兔腿_编写一个程序解鸡兔同笼问题:已知鸡兔总数为a,鸡兔腿总数为b,计算鸡兔各有多少只?...-程序员宅基地

- C++/Qt Window系统下无边框窗体_c++ 无边框窗口-程序员宅基地