老男孩读PCIe之一:从PCIe速度说起 从今天开始,老男孩要开始讲PCIe了。对我来说,这是个很大的挑战:首先,我自己本身,对PCIe并没有做到胸有成竹,我的PCIe知识也只是停留在理论阶段,我并没有实际做过任何有关...

”PCIE“ 的搜索结果

第一章 PCIE概述(上) 1.1 PCIE是什么 1.2 PCIE的链接方式 第一章 PCIE概述(上) PCIE全称peripheral component interconnect express,一个词一个词翻译就是外围设备组件互联特快,就是贼快的外围设备互联...

近期学习了 PCIe 均衡相关东西,查阅了不计其数的文档。得闲,整理一下,供个人随时查阅,亦供他人参考。PCIe 均衡系列文章分为 3 篇: 1. PCIe 均衡技术介绍(概要),简单介绍均衡的概念、信号补偿技术及均衡系数...

pcie 协议 5.0

标签: pcie5.0

开源pcie 5.0 官方文档 PCI, PCI Express, PCIe, and PCI-SIG are trademarks or registered trademarks of PCI-SIG. All other product names are trademarks, registered trademarks, or servicemarks of their ...

PCIE 1.1 总线规范,PCIE 1.1官方文档,

虚拟化 all in one 软路由 pve 硬件直通

2019 年 5 月中旬 PCI-SIG 正式发布了 PCIe 5.0 的 1.0 版本后,便马不停蹄长驱直入进入了 PCIe 6.0 的预研阶段,并在 4 个半月后发布了 PCIe 6.0 的 0.3 版本。时隔两年,现如今 PCIe 6.0 的 0.9 版本已经发布,...

Linux PCIe基础知识

PCIe 3.0 规范文档

标签: PCIe

PCIe 3.0 规范文档

PCIe(一)——基础知识

标签: fpga开发

Talking about PCIe Architecture

PCIE 接口速率查看很给力的工具

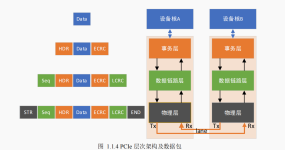

目录1. Introduction2. Transaction Layer3. Data Link Layer4. Physical Layer 1. Introduction 2. Transaction Layer 3. Data Link Layer 4. Physical Layer

PCIe总线的最大特点是像CPU访问DDR一样,可以直接使用地址访问PCIe设备(桥),但不同的是DDR和CPU同属于存储器域,而CPU和PCIe设备属于两个不同的域,PCIe设备(桥)的地址空间属于PCIe总线域。存储器域访问PCIe...

PCIe规范非常复杂,规格分为基本标准(Base)和CEM标准(Card Electromechanical),前者主要描述PCIe的基本结构、协议、链路层、物理层以及软件接口,适用于所有PCIe接口,后者重点关注PCIe接口在PCI桌面/服务器中...

PCIe 总线的数据链路层(Data Link Layer)处于事务层和物理层之间,主要进行链路管理(Link Management)、TLP错误检测,Flow Control和Link功耗管理,负责数据链路层包(Data Link Layer Packet,DLLP)的创建,...

有三个FPGA工程分别实现PCIE的三种通信模式,AXI Stream模式、memory map模式、AXI Lite模式,对应一个Qt工程实现上位机,与快速实现PCIE接口上下位机通信(二)文章内容相对应...文章与工程代码相结合,快速实现基础...

5PCI体系结构概述PCI总线的基本知识第3章PCI总线的数据交换

PCIe总线的存储器写请求、存储器读完成等TLP中含有数据负载,即Data Payload。Data Payload的长度和MPS(Max Payload Size)、MRRS(Max Read Request Size)和RCB(Read Completion Boundary)相关。RCB(Read ...

PCIe Sitch的目的主要是为了拓展PCIe接口,之前在工作中有碰到过PCIe资源不够的场景。此时,我们就可以使用PCIe Switch来扩展PCIe接口。

每个PCIE设备都有自己的独立的一段配置空间,该部分空间属于是这个设备的(可能是一段e2prom),设备在出厂时,配置空间是有默认初始值的。如上图所示,pci的配置空间是256字节,其中64字节是标准配置空间header,后面...

PCIe简介

NCB-PCI_Express_Base_6.0 NCB-PCI_Express_Base_5.0r1.0-2019-05-22 CB-PCI_Express_Base_4.0r1.0_September-29-2017-c PCI Express Base Specification Revision 3.1a ...PCIe_PHY_Test_Spec_04232019_NCB

用于研华PCIE1730数字量IO板卡的使用说明

PCIe(Peripheral Component Interconnect Express),是PCI的后继者,采用了串行通信,相比于PCI的并行通信方式,它提供了更高的传输速度和更大的带宽。通过利用 PCIe 技术的优势,这些卡提供了增强的带宽、更低的 ...

通过利用PCIe接口的高带宽和低延迟特性,我们可以实现快速的数据传输,满足高性能计算和人工智能等领域对于大规模数据处理的需求。通过合理设计硬件接口和协议,借助FPGA的强大计算能力和DMA技术的高效数据传输特性...

Xilinx-FPGA-PCIE-Linux驱动程序.rar

Xilinx linux PCIe 驱动

基于6U 6槽 VPX 高带宽PCIe的GPU AI 异构计算机以PCIe总线为架构,通过高带宽的PCIe互联,实现主控计算板、GPU AI板卡,FPGA接口板,存储板的PCIe高带宽互联访问,PCIe支持3.0规范,X8或者X16带宽。上行链路支持PCI-...

为什么需要写这篇文章,当我阅读《深入浅出SSD》这篇书籍中PCIe章节时发现,本书籍的侧重点是放在PCIe控制器和PCIe协议上,从CPU角度理解PCIe知识偏少,本文对下面几个知识点做出一些补充。 CPU访问外设寄存器与...

推荐文章

- 机器学习之超参数优化 - 网格优化方法(随机网格搜索)_网格搜索参数优化-程序员宅基地

- Lumina网络进入SDN市场-程序员宅基地

- python引用传递的区别_php传值引用的区别-程序员宅基地

- 《TCP/IP详解 卷2》 笔记: 简介_tcpip详解卷二有必要看吗-程序员宅基地

- 饺子播放器Jzvd使用过程中遇到的问题汇总-程序员宅基地

- python- flask current_app详解,与 current_app._get_current_object()的区别以及异步发送邮件实例-程序员宅基地

- 堪比ps的mac修图软件 Pixelmator Pro 2.0.6中文版 支持Silicon M1_pixelmator堆栈-程序员宅基地

- 「USACO2015」 最大流 - 树上差分_usaco 差分-程序员宅基地

- Leetcode #315: 计算右侧小于当前元素的个数_找元素右边比他小的数字-程序员宅基地

- HTTP图解读书笔记(第六章 HTTP首部)响应首部字段_web响应的首部内容-程序员宅基地