”ZYNQ“ 的搜索结果

FPGA 、ZYNQ和ZYNQ_Soc

linux3.0 device tree,包括zynq-7000,arm9,coretx-a9芯片级的所有外设驱动树,i2c,spi,dma,中断,gpio

适用于zynq7020的can调试,将库移植和软件移植可以测试can是否正常

ZYNQ 领航者FPGA开发板ZYNQ7020核心板+开发地板PDF原理图+主要器件技术手册,包括: 0-ZYNQ_7010核心板原理图_V1.5.pdf 0-ZYNQ_7020核心板原理图_V1.5.pdf 0-领航者ZYNQ底板原理图_V2.6.pdf AD9708.pdf AMS1117.pdf ...

DMA(Direct Memory Access,直接内存存取),是指外部设备不通过CPU直接与系统内存交换数据的接口技术。要将外设数据读入内存或将内存传送到外设,一般都要通过CPU控制完成,如采用查询或中断方式。...

一定要关闭MAC滤波功能,具体操作如下,1.打开 SDK 工程目录下文件 libsrc/emacps/src/xemacps.c。2.在函数 XEmacPs_Reset 中修改XEmacPs_SetOptions 函数中添加选项‐——“ XEMACPS_PROMISC_OPTION”至此,组播...

zynq的PL向PS提供时钟和复位,利用蚂蚁T9+控制板开发

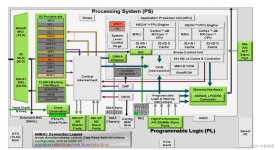

Zynq-7000 系列是赛灵思公司推出的一系列全可编程片上系统,基于 Xilinx SoC 架构。这些产品在单个设备上集成了功能丰富的双核 ARM CortexTM-A9 MPCore 处理系统(PS)和 Xilinx 可编程逻辑(PL),实现了灵活性,可配置...

本教程提供从vivado平台开始对硬件进行编程,然后倒入SDK进行嵌入式系统编程的全部详细过程,初学者可便利学习ZYNQ嵌入式系统的整体开发流程。并对SDK,vivado等软件的熟悉。

自己总结的ZYNQ程序固化的基本流程,包含从fsbl,等原理部分到具体配置流程的简述

本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中 加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。 以下为本实验原理图,CPU通过AXI BRAM Controller读取BRAM数据,...

虚拟机VMware操作系统Ubuntu编译器CMAKECmake源码OpenCV源码。

这些外设主要包括 USB 总线接口,以太网接口(ENET),SDI/SDO 接口,I2C 总线接口,CAN 总线接口,UART 接口,GPIO 等。其中BOOT.BIN是由3部分组成的(boot.elf, .bit, fsbl.elf),boot.elf这个是由交叉编译环境产生...

ZYNQ实现yolov3-tiny算法,有各个模块实现的工程及全套代码,包括下面几个部分yolo_acc,yolo_conv,yolo_max_pool,yolo_upsamp,yolo_yolo这几个模块。

zynq7020芯片手册;ug585-Zynq-7000-TRM,zynq著名手册文档ug585;官网如果太慢,可以这里下载

ZYNQ7010 / 7020_AD9363 / AD9364 / AD9361 <<<<<<< HEAD 基于ZYNQ + AD936X的开源SDR硬件 ======= ac6507f2fe1946b64a4697f9ff1226f25c21065f 基于ZYNQ + AD936X的开源SDR硬件 <<<...

PL 和PS的高效交互是zynq 7000 soc开发的重中之重,我们常常需要将PL端的大量数 据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA 的方式来进行,但是各种协议非常麻烦,灵活性也...

本文章旨在通过解读ALINX的产品——AXU2CGA/B来对ZYNQ UltraScale+ MPSoC的硬件资源有一个大致了解,完成MPSoC所涉及到的一些硬件基本概念和知识的扫盲。

本文基于zynqmp的ps端pcie2.0 x4接口功能和SSD速度测试,其中pcie2.0x4的接口上连接ssd为nvme接口的ssd盘。本文设计vivado的pcie配置、uboot设备树修改、kernel源码修改以及基于dd命令进行NVMe的ssd读写速度的测试。...

Zynq AXIS:完整的DMA系统 此存储库包含使用Xilinx的Zynq FPGA建立基于DMA的项目所需的所有组件。 首先,有一个称为AXIS的硬件模块,可连接到高性能AXI接口端口。 其次,有一个Linux UIO驱动程序,可将低级AXIS控制...

Zynq 是 Xilinx 公司提出的全可编程 SoC 架构,集成了单核或多核 ARM 处理器与 Xilinx 16nm 或 28nm 可编程逻辑,包括 Zynq 7000 Soc,Zynq UltraScale+ MPSoC 和 Zync UltraScale+ RFSoC 等系列。本文主要介绍 ...

本文介绍自定义IP核实现呼吸灯实验,文中给出了具体的创建过程,还给出了固化程序的两种方式。

Zynq DMA Linux 驱动程序 该 Linux 驱动程序已开发为可在 Xilinx Zynq FPGA 上运行。 它是一个包装驱动程序,用于与低级 Xilinx 驱动程序 (xilinx_axidma.c) 对话,该驱动程序连接到在 Zynq FPGA 的 PL 部分中实现的...

采集外部设备的电压值,用FPGA内部自带的XADC

本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。以下为本实验原理图,CPU通过AXI BRAM Controller读取BRAM数据,CPU...

我们提供了完整的工程代码,包括Python网络训练、权值文件和测试文件导出,以及vivado、SDK和Vitis...我们在ZYNQ开发板上进行了实验,测试了基于CNN和BP神经网络的本地图像识别系统在不同数据集上的准确率和处理速度。

ZYNQ UltraScale+ MPSoc ZU5EV核心板原理图, Zynq UltraScale+MPSoC是Xilinx推出的第二代多处理SoC系统,它在第一代Zynq-7000的基础上进行了全面升级。 该芯片基于业内最先进的16nm FinFET+工艺制程打造,整合了64...

推荐文章

- SMT的基本知识介绍_smt行业基础知识-程序员宅基地

- 43.基于SSM的口腔护理网站|基于SSM框架+ Mysql+Java设计与实现(可运行源码+数据库+lw)-程序员宅基地

- HTML中Table表格的使用与漂亮的表格模板_html table 样式-程序员宅基地

- Linkage Mapper中的局部和全局地图比较实践指南(含实例分析)-程序员宅基地

- 线性筛求欧拉函数-程序员宅基地

- 初中几何题_初中几何题解-程序员宅基地

- jQuery 放大镜效果_jquery放大效果-程序员宅基地

- Python构建快速高效的中文文字识别OCR_中文ocr python-程序员宅基地

- SQL语句用case when实现if-else条件逻辑_case when里面可以加if else吗-程序员宅基地

- 数据结构实验课程设计报告求工程的最短完成时间_(1)用字符文件提供数据建立aoe网络邻接表存储结构; (2)编写程序,实现图中顶点的-程序员宅基地