”可配置逻辑块CLB“ 的搜索结果

随着数字电路设计和嵌入式系统应用的不断发展,FPGA(Field-Programmable Gate Array)作为一种灵活、可重构的可编程逻辑器件,受到了越来越广泛的关注和应用。本篇博客将探讨FPGA的原理、架构及底层资源,旨在为...

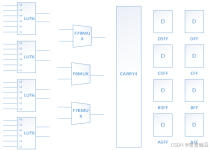

1、查找表(LUT) (组合逻辑单元) LUT指显示查找表(Look-Up-Table),本质上就是一个RAM。它把数据事先写入RAM后,每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。 2、D 触发器 ...

QX320F280049C,特性: 1、C28x内核+CLA浮点协处理内核,32位双核CPU,高频...9、可配置逻辑块(CLB) 优点:1、32位双核,主频高达100MHz 2、3个12位ADC,采样率高达3.45MSPS 3、价格便宜 4、pin2pin替代TMS320F280049C

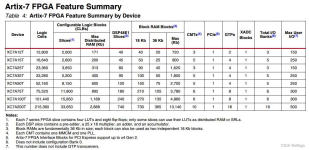

赛灵思 7系列 FPGA CLB资源介绍

本文针对Vivado中实现的逻辑锁定和增量编译进行的工程实例介绍,文中有对应工程的下载地址。友情提示:(1)增量编译只允许修改当前工程不超过5%的时候才有效,一般应用于较大工程添加修改chipscope监测信号使用;(2)...

FPGA的作用与简介

标签: FPGAIC

一个 FPGA 芯片的内部资源包括一个被 I/O 组块环围的可配置 逻辑组块(CLB)矩阵。在 FPGA 矩阵内,信号通过可编程的互连开关和连线传递。 CompactRIO 入门教程 2 CompactRIO 入 门 教 程 图 2.FPGA 芯片的内部构造

FPGA即现场可编程门阵列,其结构与传统的门阵列相似,大量的可编程逻辑块( CLB , Configurable Logic Block ) 在芯片中央按矩阵排列,芯片四周为可编程输入/输出块( IOB , Input / Output Block),CLB行列之间及CLB和...

实验准备课。

是基于通过可编程互连连接的可配置逻辑块(CLB)矩阵的半导体器件。 在制造后,可以将FPGA重新编程为所需的应用程序或功能要求。 是一种新的系列板,价格低廉,外形小巧。 FPGA工具 是LabVIEW的软件附件,可用于通过...

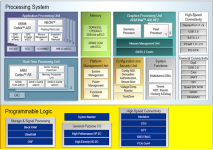

ARM,DSP,FPGA概念 ...ARM架构是面向低预算市场设计的第一款RISC微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,四个功能模块可供生产厂商根据不同用户要求来

此FPGA逻辑资源丰富,其内有30万个系统门,6912个逻辑单元(LC),1536个可配置逻辑快(CLB),64Kbit的块RAM,146个可用的I/O口,4个数字延迟锁相环(DLL)。块RAM可实现大量数据的内部存储,延迟锁相环可对时钟进行管理...

数字集成电路有全定制、门阵列、标准单元、可编程器件、微处理器和SoC等多种实现方式,需根据性能要求、研发周期、经济性、灵活性等要求权衡选择

FPGA中的基础单元--AlteraAltera FPGA的组成部分LAB逻辑阵列方块MLABALM可编程逻辑单元LUT查找表Adder加法器Register寄存器Embedded Memory Blocks嵌入式存储模块Digital Signal Processing (DSP)数字信号处理器...

FPGA基本内部结构

标签: fpga

l 可配置逻辑单元 Configurable Logic Blocks (CLB) l Bram Block SelectRAM l 18 x 18 乘法器 (18-Bit x 18-Bit Multipliers) l 全局时钟网络 (Global Clock Mux) l 数字时钟管理模块 (DCM) l 布线资源 ...

LUT还可轻松执行在可配置逻辑块(CLB)芯片,以及嵌入式乘法单元或DSP48可编程乘法累加(MAC)单元方面可能要求过多FPGA资源的复杂数学函数。 不过,以这种方式使用LUT当然也会存在一些弊端。当您使用...

可配置逻辑单元 2.1 6输入查找表(LUT6) 2.2 选择器(MUX) 2.3 进位链(Carry Chain) 2.4 触发器(Flip-Flop) 参考文献: 一直以来,觉得自己关于FPGA方面,摸不到“低”——对底层架构认识不清,够...

海思、中兴微电子、联发科、紫光系列、兆易创新、长江存储、芯原微电子、哲库、平头哥、汇顶、Pinctrl子系统、I2C子系统、中断子系统、块设备驱动框架、Bootloader等。地平线机器人、黑芝麻智能、寒武纪、摩尔线程、...

# 1. FPGA简介和基本概念 FPGA(Field-Programmable Gate Array)是一种现场可编程门阵列,是集成电路的一种,它的内部电路可以通过用户编程来实现特定...其结构包括配置存储器、可编程逻辑单元(CLB)、输入输出块

推荐文章

- C++语法基础--标准库类型--bitset-程序员宅基地

- [C++] 第三方线程池库BS::thread_pool介绍和使用-程序员宅基地

- 如何使用openssl dgst生成哈希、签名、验签-程序员宅基地

- ios---剪裁圆形图片方法_ios软件圆形剪裁-程序员宅基地

- No module named 'matplotlib.finance'及name 'candlestick_ochl' is not defined强力解决办法-程序员宅基地

- 基于java快递代取计算机毕业设计源码+系统+lw文档+mysql数据库+调试部署_快递企业涉及到的计算机语言-程序员宅基地

- RedisTemplate与zset redis_redistemplate zset-程序员宅基地

- 服务器虚拟化培训计划,vmware虚拟机使用培训(一)概要.ppt-程序员宅基地

- application/x-www-form-urlencoded方式对post请求传参-程序员宅基地

- 网络安全常见十大漏洞总结(原理、危害、防御)-程序员宅基地