”可配置逻辑块CLB“ 的搜索结果

由于 CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。到90年代,CPLD发展更为迅速,不仅具有电擦除特性,而且出现了边缘扫描及...

FPGA工程师笔面试-整理背诵版

标签: fpga

整理归纳FPGA工程师笔面试的知识准备-自用

FPGA是由通过可编程互连连接的可配置逻辑块 (CLB) 矩阵构成的可编程半导体器件。相对于专为特定设计定制构建的专用集成电路 (ASIC)而言,FPGA 能通过编程来满足应用和功能要求。 虽然市面上也有一次性可编程 (OTP)...

FPGA中的DRAM,DRAM的配置方式,DRAM的原理与结构,DRAM的实现方式,vivado推断DRAM和BRAM,Distributed RAM

CLB(包括LUT、加法器、寄存器、MUX(多路选择器)) 时钟网络资源(全局时钟网络,区域时钟网络,IO时钟网络),理解时钟网络的本质和意义 时钟处理单元(PLL,DCM),理解时钟网络资源和时钟处理单元的差异和...

CLB在FPGA中最为丰富,由两个slice(片)构成:SLICEL(L:logic) 和SLICEM(M:memory)之分,因此CLB可分为CLBLL和CLBLM两类。一个芯片差不多2/3是SLICEL,1/3是SLICEM。 SLICEL和SLICEM内部都包含4个6输入查找表.....

FPGA内部最主要的、最需要关注的部件是CLB(Configurable Logic Block,可配置逻辑块)、Input/Output Block(输入/输出块)和BlockRAM(块RAM)。 CLB是FPGA具有可编程能力的主要承担者。通过配置这些CLB可...

FPGA的主要组成部分有可编程逻辑单元(CLB)、输入输出块(IOB)、互连网络以及全局时钟管理等模块。 1. 可编程逻辑单元(CLB):CLB是FPGA中最基本的逻辑单元,可以实现与、或、非等逻辑运算。CLB由输入输出引脚、...

本文详细介绍了构成FPGA的多种结构以及这些结构如何相互合作实现特定功能。 传送门:FPGA可编程技术 ...实现逻辑电路的逻辑要素 —— 逻辑块(Logic Block,LB)。此要素以触发器和门电路为底层单元

前沿技术早知道,弯道超车有希望积累超车资本,从关注DD开始图文编辑:xj、来源:网络如何您是一名创业公司的负责人,如何从0搭建公司的后端技术栈。今天要说的后台是大后台的概念,放在服务器上...

可配置逻辑块(configurable logic block,CLB)是一种提供高级、高性能的FPGA逻辑的组件。它包含了多个功能单元,如6输入查找表(LUT)、分布式内存、移位寄存器和算术单元等。\[1\] CLB的基本结构是由四个6输入LUT...

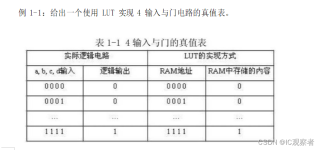

FPGA原理与结构,LUT的基本组成原理和应用,LUT的发展历史,为什么流行使用6-LUT

目录 1. PLD的发展历程 2. 半导体存储器的分类 3. PLD的分类 4. FPGA厂商 5. FPGA的结构 ...5.1Altera Cyclone IV为例 ...这些是对之前的笔记做了个总结,主要是了解FPGA的内部结构,开发流程以及常用的工具等知识。...

信号处理和电信马蒂斯博士学校提交人ChristopheHURI aU x在IRISA研究单位(UMR 6074)计算机科学和随机系统研究所编写国立应用科学技术高等增强型FPGA架构高效的CAD流程运行时硬件重新配置论文答辩于2015年陪审团由...

ALM:Adaptive Logic Modules 自适应逻辑块 LAB:Logic Array Blocks 逻辑阵列块 首先FPGA芯片主要由三部分...(2) LAB(logic array block,逻辑阵列块,对于Xilinx称之为可配置逻辑块CLB); (3) Interconnect(内...

1 、wire型和reg型 wire网线型表示硬件单元之间的连线,值由驱动单元决定,缺省值是高阻值z。模块的输入输出信号数据类型默认为wire型。 reg寄存器型表示一个抽象的数据储存单元,只能在always和initial语句中用<...

FPGA组成、工作原理和开发流程 备注:下面的描述基于ALTERA系列的FPGA芯片,而且...FPGA是英文FieldProgrammableGateArray的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发...

FPGA即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编辑器件门电路数有限...

********************************LoongEmbedded******************************** 作者:LoongEmbedded(kandi) 时间:2012.1.7 类别:FPGA开发 ********************************LoongEmbedded***************...

2.9 实现 现代数字电路设计师依靠CAD工具来将设计模型翻译成实现数据。数字设计CAD工具将数字电路的描述综合(翻译)成优化过和对技术依赖的门级描述,称为网表。特定用途的集成芯片(ASIC)和FPGA都是非定制IC技术...

推荐文章

- 1N5819-ASEMI轴向肖特基二极管1N5819-程序员宅基地

- 把maven的setting配置文件改为需要jdk版本_<profile> <id>jdk-1.4</id> <activation> <jdk>1.4</-程序员宅基地

- 使用matlab进行DBscan聚类_dbscan聚类分析图用什么软件-程序员宅基地

- 探秘技术新星:BBS_admin - 一个现代化的论坛后台管理系统-程序员宅基地

- 【译】JavaScript 开发者年度调查报告-程序员宅基地

- 神仙级渗透测试入门教程(非常详细),从零基础入门到精通,从看这篇开始!_网络渗透技术自学-程序员宅基地

- 多个protocbuf版本切换_protobuf调整版本-程序员宅基地

- msf+cobaltstrike联动(一):把msf的session发给cobaltstrike-程序员宅基地

- C语言--编写程序,输入一个整数,判断它能否被3,5,7整除_编程序实现功能:输入一个整数,判断其是否能同时被3、5、7整除。能被整除则输出“y-程序员宅基地

- 数据技术之Hadoop(HFDS文件系统)-程序员宅基地