即使是非常有经验的Verilog设计人员也不能完全理解在IEEE兼容的Verilog模拟器中如何安排非阻塞分配,并且不了解应该何时以及为何应该使用非阻塞赋值。 本文详细介绍了如何安排Verilog阻塞和非阻塞赋值,提供重要的...

”非阻塞赋值“ 的搜索结果

阻塞赋值和非阻塞赋值

本文介绍了Verilog阻塞与非阻塞赋值的区别

verilog阻塞和非阻塞赋值语句

阻塞赋值与非阻塞赋值

标签: Verilog

阻塞赋值的执行可以认为是只有一个步骤的操作,即计算RHS并更新LHS,且不允许其他语句的干扰。

硅芯思见:阻塞赋值与非阻塞赋值

标签: 开发语言

FPGA中阻塞赋值与非阻塞赋值原理实验 fpga开发.pdf

文章主要介绍Verilog中阻塞赋值和非阻塞赋值的正确使用方法。

阻塞赋值和非阻塞赋值的区别

标签: fpga开发

最近学到了关于verilog的阻塞赋值与非阻塞赋值的一些区别,经过网上查阅与仿真实验,有了一些理解。希望能够记下来。

非阻塞赋值和阻塞赋值很好区分,大家只要搞清楚这两点,前期思维转换过来需要点时间,但写代码越多,就越容易理解。1、逻辑上非阻塞赋值可以理解成时钟发生边沿变化时,即更新新的计算结果;阻塞赋值可以理解成计算...

FPGA的阻塞赋值与非阻塞赋值

标签: FPGA

阻塞赋值&非阻塞赋值

标签: fpga开发

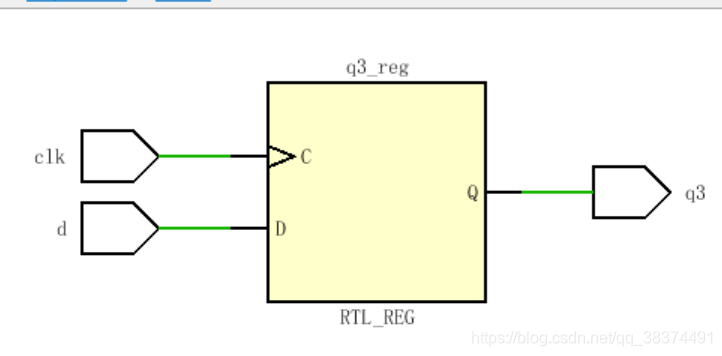

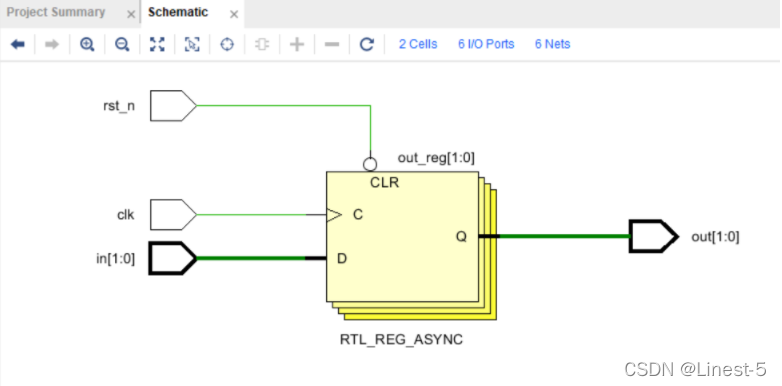

阻塞赋值的符号用 “=” 表示,对应的电路结构往往与触发沿没有关系,只与输入电平的变化有关系。它的操作可以认为是只有一个步骤的操作,即计算赋值号右边的语句并更新赋值号左边的语句,此时不允许有来自其他...

阻塞赋值操作符用等号(即 = )表示。为什么称这种赋值为阻塞赋值呢?这是因为在赋值时先计算等号右手方向(RHS)部分的值,只是赋值语句不允许任何别的Verilog语句的干扰,直到现行的赋值完成时刻,即把RHS赋值给...

本文转自知乎罗成的文章Verilog语法之六:阻塞赋值与非阻塞赋值 总的文章小白如何快速入门Verilog 本文首发于微信公众号“花蚂蚁”,想要学习FPGA及Verilog的同学可以关注一下。 一、初步理解阻塞赋值与非阻塞赋值 ...

阻塞赋值和非阻塞赋值(一)

标签: fpga开发

Verilog阻塞与非阻塞赋值详解

在Verilog HDL语言中,信号有两种赋值方式,即阻塞赋值和非阻塞赋值。 1、阻塞(Blocking)赋值(如 b = a) 阻塞赋值,顾名思义,即在一个always块中,后面的语句会受到前语句的影响,具体来说,在同一个always中...

推荐文章

- 『Android 技能篇』优雅的转场动画之 Transition-程序员宅基地

- Webshell绕过技巧分析之-base64编码和压缩编码-程序员宅基地

- 大一计算机思维知识点,大学计算机—基于计算思维知识点详解.docx-程序员宅基地

- 关于敏捷开发的一篇访谈录-程序员宅基地

- 挑战安卓和iOS!刚刚,华为官宣鸿蒙手机版,P40搭载演示曝光!高管现场表态:我们准备好了...-程序员宅基地

- 精选了20个Python实战项目(附源码),拿走就用!-程序员宅基地

- android在线图标生成工具,图标在线生成工具Android Asset Studio的使用-程序员宅基地

- android 无限轮播的广告位_轮播广告位-程序员宅基地

- echart省会流向图(物流运输、地图)_java+echart地图+物流跟踪-程序员宅基地

- Ceph源码解析:读写流程_ceph 发送数据到其他副本的源码-程序员宅基地