FPGA-LCD基础驱动_fpga lcd cnt-程序员宅基地

技术标签: # FPGA学习篇

LCD的接口时序波形如图所示。VSYNC是场同步信号,低电平有效,从时序图可以看出,VSYNC是每一场(即也可以理解为每送一幅完整图像)的同步信号;与此类似,HSYNC是行同步信号,也是在每一行数据传输的开始产生几个时钟周期的低脉冲。这两个信号用于同步当前的数据信号,根据固定的脉冲约定,我们在某些时钟上升沿前将图像数据送到数据总线上供LCD内部锁存。

LCD驱动时序波形

这是LCD时序图中对应的时间参数。

表8.11 LCD驱动时序参数表

| 信号 |

列项 |

标记 |

最小值 |

标准值 |

最大值 |

单位 |

| Dclk |

频率 |

Tosc |

156 |

ns |

||

| 最大时间 |

Tch |

78 |

ns |

|||

| 最小时间 |

Tcl |

78 |

ns |

|||

| Data |

建立时间 |

Tsu |

12 |

ns |

||

| 保持时间 |

Thd |

12 |

ns |

|||

| Hsync |

周期 |

TH |

408 |

Tosc |

||

| 脉冲宽度 |

THS |

5 |

30 |

Tosc |

||

| 后沿 |

THB |

38 |

Tosc |

|||

| 显示周期 |

TEP |

320 |

Tosc |

|||

| 同步周期 |

THE |

36 |

68 |

88 |

Tosc |

|

| 前沿 |

THF |

20 |

Tosc |

|||

| Vsync |

周期 |

TV |

262 |

TH |

||

| 脉冲宽度 |

TVS |

1 |

3 |

5 |

TH |

|

| 后沿 |

TVB |

15 |

TH |

|||

| 显示周期 |

TVD |

240 |

TH |

|||

| 前沿 |

TVF |

2 |

4 |

TH |

相同的方式驱动的程序写法类似:

顶层文件:

module top(ext_clk_25m,ext_rst_n,lcd_light_en,lcd_clk,lcd_hsy,lcd_vsy,lcd_r,lcd_g,lcd_b

);

input ext_clk_25m;

input ext_rst_n;

output lcd_light_en;

output lcd_clk;

output lcd_hsy;

output lcd_vsy;

output [4:0] lcd_r;

output [5:0] lcd_g;

output [4:0] lcd_b;

lcd_controller uut_lcd_controller(

.clk(ext_clk_25m),

.rst_n(ext_rst_n),

.lcd_light_en(lcd_light_en),

.lcd_clk(lcd_clk),

.lcd_hsy(lcd_hsy),

.lcd_vsy(lcd_vsy),

.lcd_r(lcd_r),

.lcd_g(lcd_g),

.lcd_b(lcd_b)

);

endmodule

lcd_controller.v

module lcd_controller(clk,rst_n,lcd_light_en,lcd_clk,lcd_hsy,lcd_vsy,lcd_r,lcd_g,lcd_b

);

input clk;

input rst_n;

output lcd_light_en;

output lcd_clk;

output reg lcd_hsy;

output reg lcd_vsy;

output [4:0] lcd_r;

output [5:0] lcd_g;

output [4:0] lcd_b;

parameter HSY_TH=9'D408-1'D1;//周期

parameter HSY_THS=9'D30 ;//脉冲宽度

parameter HSY_THB=9'D38 ;//后沿

parameter HSY_TEP=9'D320 ;//显示周期

parameter HSY_THE=9'D68 ;//同步周期

parameter HSY_THF=9'D20 ;//前沿

parameter VSY_TV=9'D262-1'D1;//周期

parameter VSY_TVS=9'D3 ;//脉冲宽度

parameter VSY_TVB=9'D15 ;//后沿

parameter VSY_TVD=9'D240 ;//显示周期

parameter VSY_TVF=9'D4 ;//前沿

//lcd背光常开

assign lcd_light_en=1'b1;

//配置驱动时钟6.25mHz

reg [1:0] lcd_cnt;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_cnt<=1'b0;

end

else begin

lcd_cnt<=lcd_cnt+1'b1;

end

end

assign lcd_clk=lcd_cnt[1];

wire dchange ={lcd_cnt==2'd2};

//X和Y轴计数器

reg[8:0] xcnt;

reg[8:0] ycnt;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

xcnt<=1'b0;

end

else if(dchange==1'b1)begin

if(xcnt==HSY_TH)begin

xcnt<=1'b0;

end

else begin

xcnt<=xcnt+1'b1;

end

end

else;

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

ycnt<=1'b0;

end

else if(dchange&&xcnt==HSY_TH)begin

if(ycnt==VSY_TV)begin

ycnt<=1'b0;

end

else begin

ycnt<=ycnt+1'b1;

end

end

else begin

ycnt<=ycnt;

end

end

//lcd显示的有效区域

reg valid;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

valid<=1'b0;

end

else if(ycnt>=(VSY_TVS+VSY_TVB)&&ycnt<(VSY_TVS+VSY_TVB+VSY_TVD)&&

xcnt>=(HSY_THS+HSY_THB)&&xcnt<(HSY_TEP+HSY_THB+HSY_THE))begin

valid<=1'b1;

end

else begin

valid<=1'b0;

end

end

//LCD驱动行场同步信号产生逻辑

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_hsy<=1'b1;

end

else if(xcnt==1'b0)begin

lcd_hsy<=1'b0;

end

else if(xcnt>=HSY_THS)begin

lcd_hsy<=1'b1;

end

else begin

lcd_hsy<=lcd_hsy;

end

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_vsy<=1'b1;

end

else if(ycnt==1'b0)begin

lcd_vsy<=1'b0;

end

else if(ycnt>=VSY_TVS)begin

lcd_vsy<=1'b1;

end

else begin

lcd_vsy<=lcd_vsy;

end

end

//产生显示条纹

reg [3:0]tmp_cnt;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

tmp_cnt<=1'b0;

end

else if(valid==1'b0)begin

tmp_cnt<=1'b0;

end

else if(valid&&dchange)begin

if(tmp_cnt<4'd9)begin

tmp_cnt<=tmp_cnt+1'b1;

end

else begin

tmp_cnt<=1'b0;

end

end

end

reg [15:0]lcd_db_rgb;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_db_rgb<=16'd0;

end

else if(valid)begin

if((tmp_cnt==4'd9)&&dchange)begin

lcd_db_rgb[15:11]<=lcd_db_rgb[15:11]+1'b1;

end

else;

end

else begin

lcd_db_rgb<=1'b0;

end

end

assign lcd_r =valid ? lcd_db_rgb[15:11]:5'd0;

assign lcd_g =valid ? lcd_db_rgb[10:5]:6'd0;

assign lcd_b =valid ? lcd_db_rgb[4:0]:5'd0;

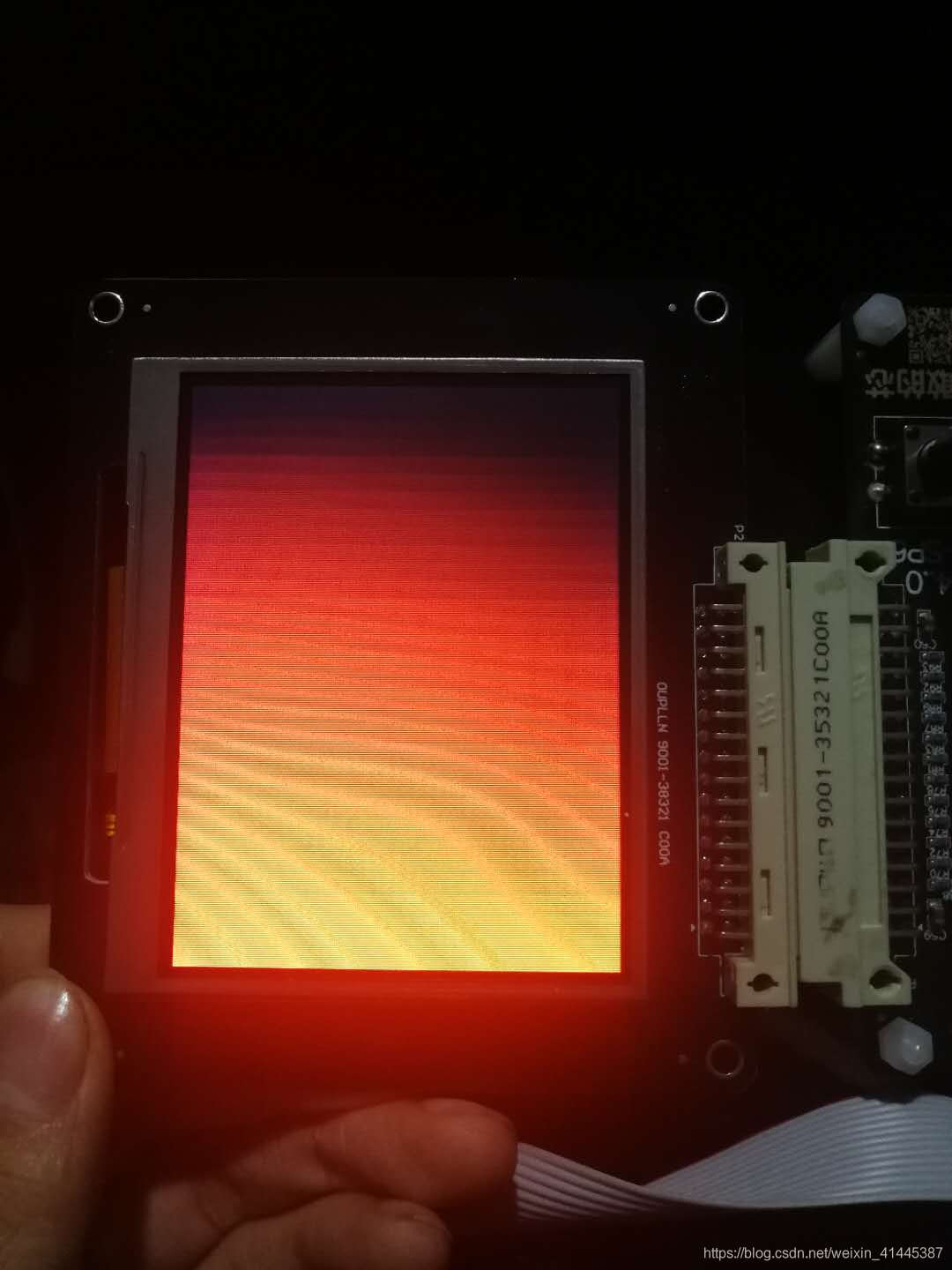

endmodule下板子效果图:

智能推荐

51单片机的中断系统_51单片机中断篇-程序员宅基地

文章浏览阅读3.3k次,点赞7次,收藏39次。CPU 执行现行程序的过程中,出现某些急需处理的异常情况或特殊请求,CPU暂时中止现行程序,而转去对异常情况或特殊请求进行处理,处理完毕后再返回现行程序断点处,继续执行原程序。void 函数名(void) interrupt n using m {中断函数内容 //尽量精简 }编译器会把该函数转化为中断函数,表示中断源编号为n,中断源对应一个中断入口地址,而中断入口地址的内容为跳转指令,转入本函数。using m用于指定本函数内部使用的工作寄存器组,m取值为0~3。该修饰符可省略,由编译器自动分配。_51单片机中断篇

oracle项目经验求职,网络工程师简历中的项目经验怎么写-程序员宅基地

文章浏览阅读396次。项目经验(案例一)项目时间:2009-10 - 2009-12项目名称:中驰别克信息化管理整改完善项目描述:项目介绍一,建立中驰别克硬件档案(PC,服务器,网络设备,办公设备等)二,建立中驰别克软件档案(每台PC安装的软件,财务,HR,OA,专用系统等)三,能过建立的档案对中驰别克信息化办公环境优化(合理使用ADSL宽带资源,对域进行调整,对文件服务器进行优化,对共享打印机进行调整)四,优化完成后..._网络工程师项目经历

LVS四层负载均衡集群-程序员宅基地

文章浏览阅读1k次,点赞31次,收藏30次。LVS:Linux Virtual Server,负载调度器,内核集成, 阿里的四层SLB(Server Load Balance)是基于LVS+keepalived实现。NATTUNDR优点端口转换WAN性能最好缺点性能瓶颈服务器支持隧道模式不支持跨网段真实服务器要求anyTunneling支持网络private(私网)LAN/WAN(私网/公网)LAN(私网)真实服务器数量High (100)High (100)真实服务器网关lvs内网地址。

「技术综述」一文道尽传统图像降噪方法_噪声很大的图片可以降噪吗-程序员宅基地

文章浏览阅读899次。https://www.toutiao.com/a6713171323893318151/作者 | 黄小邪/言有三编辑 | 黄小邪/言有三图像预处理算法的好坏直接关系到后续图像处理的效果,如图像分割、目标识别、边缘提取等,为了获取高质量的数字图像,很多时候都需要对图像进行降噪处理,尽可能的保持原始信息完整性(即主要特征)的同时,又能够去除信号中无用的信息。并且,降噪还引出了一..._噪声很大的图片可以降噪吗

Effective Java 【对于所有对象都通用的方法】第13条 谨慎地覆盖clone_为继承设计类有两种选择,但无论选择其中的-程序员宅基地

文章浏览阅读152次。目录谨慎地覆盖cloneCloneable接口并没有包含任何方法,那么它到底有什么作用呢?Object类中的clone()方法如何重写好一个clone()方法1.对于数组类型我可以采用clone()方法的递归2.如果对象是非数组,建议提供拷贝构造器(copy constructor)或者拷贝工厂(copy factory)3.如果为线程安全的类重写clone()方法4.如果为需要被继承的类重写clone()方法总结谨慎地覆盖cloneCloneable接口地目的是作为对象的一个mixin接口(详见第20_为继承设计类有两种选择,但无论选择其中的

毕业设计 基于协同过滤的电影推荐系统-程序员宅基地

文章浏览阅读958次,点赞21次,收藏24次。今天学长向大家分享一个毕业设计项目基于协同过滤的电影推荐系统项目运行效果:项目获取:https://gitee.com/assistant-a/project-sharing21世纪是信息化时代,随着信息技术和网络技术的发展,信息化已经渗透到人们日常生活的各个方面,人们可以随时随地浏览到海量信息,但是这些大量信息千差万别,需要费事费力的筛选、甄别自己喜欢或者感兴趣的数据。对网络电影服务来说,需要用到优秀的协同过滤推荐功能去辅助整个系统。系统基于Python技术,使用UML建模,采用Django框架组合进行设

随便推点

你想要的10G SFP+光模块大全都在这里-程序员宅基地

文章浏览阅读614次。10G SFP+光模块被广泛应用于10G以太网中,在下一代移动网络、固定接入网、城域网、以及数据中心等领域非常常见。下面易天光通信(ETU-LINK)就为大家一一盘点下10G SFP+光模块都有哪些吧。一、10G SFP+双纤光模块10G SFP+双纤光模块是一种常规的光模块,有两个LC光纤接口,传输距离最远可达100公里,常用的10G SFP+双纤光模块有10G SFP+ SR、10G SFP+ LR,其中10G SFP+ SR的传输距离为300米,10G SFP+ LR的传输距离为10公里。_10g sfp+

计算机毕业设计Node.js+Vue基于Web美食网站设计(程序+源码+LW+部署)_基于vue美食网站源码-程序员宅基地

文章浏览阅读239次。该项目含有源码、文档、程序、数据库、配套开发软件、软件安装教程。欢迎交流项目运行环境配置:项目技术:Express框架 + Node.js+ Vue 等等组成,B/S模式 +Vscode管理+前后端分离等等。环境需要1.运行环境:最好是Nodejs最新版,我们在这个版本上开发的。其他版本理论上也可以。2.开发环境:Vscode或HbuilderX都可以。推荐HbuilderX;3.mysql环境:建议是用5.7版本均可4.硬件环境:windows 7/8/10 1G内存以上;_基于vue美食网站源码

oldwain随便写@hexun-程序员宅基地

文章浏览阅读62次。oldwain随便写@hexun链接:http://oldwain.blog.hexun.com/ ...

渗透测试-SQL注入-SQLMap工具_sqlmap拖库-程序员宅基地

文章浏览阅读843次,点赞16次,收藏22次。用这个工具扫描其它网站时,要注意法律问题,同时也比较慢,所以我们以之前写的登录页面为例子扫描。_sqlmap拖库

origin三图合一_神教程:Origin也能玩转图片拼接组合排版-程序员宅基地

文章浏览阅读1.5w次,点赞5次,收藏38次。Origin也能玩转图片的拼接组合排版谭编(华南师范大学学报编辑部,广州 510631)通常,我们利用Origin软件能非常快捷地绘制出一张单独的绘图。但是,我们在论文的撰写过程中,经常需要将多种科学实验图片(电镜图、示意图、曲线图等)组合在一张图片中。大多数人都是采用PPT、Adobe Illustrator、CorelDraw等软件对多种不同类型的图进行拼接的。那么,利用Origin软件能否实..._origin怎么把三个图做到一张图上

51单片机智能电风扇控制系统proteus仿真设计( 仿真+程序+原理图+报告+讲解视频)_电风扇模拟控制系统设计-程序员宅基地

文章浏览阅读4.2k次,点赞4次,收藏51次。51单片机智能电风扇控制系统仿真设计( proteus仿真+程序+原理图+报告+讲解视频)仿真图proteus7.8及以上 程序编译器:keil 4/keil 5 编程语言:C语言 设计编号:S0042。_电风扇模拟控制系统设计