我们先来看看时序分析器如何打开,单独运行版本,可以从ISE的程序启动目录下打开,如图1所示。 图1 启动单独运行时序分柝器 打开时序分析器后,需要指定NCD设计文件和PCF约束文件。如果要做Post-MAP(映射后)...

”使用时序分析器“ 的搜索结果

我们先来看看时序分析器如何打开,单独运行版本,可以从ISE的程序启动目录下打开,如图1所示。 图1 启动单独运行时序分柝器 打开时序分析器后,需要指定NCD设计文件和PCF约束文件。如果要做Post-MAP(映射后)...

时序分析器可以从ISE工程中打开,在【Processes】窗口中展开【Map】目录,双击【AnalyzePostˉMAP Static Timing】图标打开时序分析器. 也可以展开【Place & Route】目录,然后双击【Analyze Post Place & Route ...

时序分析器的用户界面

标签: 时序分析器的用户界面

时序分析器可以从ISE工程中打开,在【Processes】窗口中展开【Map】目录,双击【AnalyzePostˉMAP Static Timing】图标打开时序分析器. 也可以展开【Place & Route】目录,然后双击【Analyze Post Place & Route ...

使用Quartus II Timequest时序分析器约束分析 设计

使用逻辑分析仪抓取的一定位对一脉冲或两定位对一脉冲两种EC11旋转编码器的时序图。包括正转,反转,连续正转,连续反转时序。

静态时序分析器用Python实现的逻辑电路静态时序分析器 :electric_plug: :high_voltage: (2018) 该分析器实现了几个部分,并输出HTML files 。 它在从Verilog & C创建的自定义设计获得的门级网表上起作用。 使用...

使用Quartus II Timequest时序分析器约束分析设计 Quartus II的项目,并把所有需要的设计文件都加入到项目中...在编译过程中,软件会优化设计的逻辑、布局布线等来尽可能满足所有

如果设备出现故障,要进行系统调试,一种方法是先查找毛刺。毛刺是非常窄的脉冲,毛刺在系统中可能导致、也可能不导致逻辑...毛刺可以是多种设备故障(包括竞争情况、端接错误、驱动器错误、时序违规和串扰)的最初迹象。

kta:KTH的时序分析器

标签: C

KTA KTA(KTH的时序分析器)是用于C和机器代码的静态分析的工具。 当前,仅支持MIPS32 ISA。 当前版本的KTA可以执行两种类型的分析: 交互式时序分析:该工具将.ta时序分析文件作为输入,其中包含有关应进行哪种分析...

Timing Analyzer 在全编译期间对设计自动进行时序分析。 以下准则描述了 使用 Quartus II Timing Analyzer 可以完成的一些任务: 使用 定时设置向导(Assignments 菜单)、Settings 对话框 (Assignments 菜单)和 ...

可以快速入手使用LA5016便携式逻辑分析。...在针对单片机、嵌入式、FPGA、DSP等数字系统的测量测试时,相比于示波器,逻辑分析仪可以提供更佳的时序精确度、更强大的逻辑分析手段以及大得多的数据采集量。

但如果用了这一功能,30s之内即可搞定I2C时序分析软件。此功能ZDS全系列示波器均可升级! 1、I2C总线介绍 I2C总线是PHLIPS公司推出的一种串行总线,是具备多主机系统所需的包括总线裁决和高低速器件...

逻辑分析仪软件Kingst VIS+使用手册。非常适合不了解和刚准备入门逻辑分析仪的小伙伴。

1.提高设计的工作频率 2.获得正确的时序分析报告 3.指定 FPGA/CPLD 引脚位置与电气标准 1.时钟约束必须最早创建,对 7 系列 FPGA 来说,端

分析spi时序

由于逻辑分析仪不像示波器那样有许多电压等级,通常只显示两个电压(逻辑1和0),因此设定了参考电压后,逻辑分析仪将被测信号通过比较器进行判定,高于参考电压者为High,低于参考电压者为Low,在High与 Low之间...

ASIC芯片设计静态时序分析(STA)验证综合编程规范IC设计与方法等文档资料: ASIC Guide from Atmel.pdf asic_design_guide.pdf ASIC中的异步时序设计.doc ASIC设计教程.pdf asynchronous signals in a synchronous ...

用visio画时序分析波形图,下载后只要在这个visio文件里复制、粘贴、编辑下就能用了,很方便。

本文由本人原创翻译于ALTERA的官网上Educational_Materials->Digital_Logic->Tutorials->Timing_Analysis_Tutorials下一篇名为Using TimeQuest Timing Analyzer的文章,个人觉得ALTERA官网上很多教程都很不错,有...

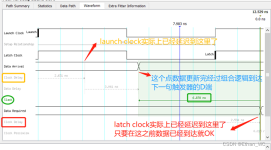

据个人理解区分静态时序分析和动态时序分析,是在于在分析电路时序时有没有输入激励。STA分析就是通过时序库文件给出的各条时序路径的延迟,来确认在每个FF上是否满足建立/保持时间。而DTA就需要给设计灌入激励在...

继“时序分析”基础篇的基础上,着重阐述如何利用“quartus ii Timequest 工具进行时序约束,时序分析和时序验证,属于时序分析的晋级篇。

通过Quartu自带例程fir_filter进行学习如何使用Timing Analyzer进行时序分析与约束。

但如果用了这一功能,30s之内即可搞定I2C时序分析软件。此功能ZDS全系列示波器均可免费升级! 1、I2C总线介绍 I2C总线是PHLIPS公司推出的一种串行总线,是具备多主机系统所需的包括总线裁决和高低速...

随着FPGA技术的广泛使用,越来越需要一台能够测试验证FPGA芯片中所下载电路逻辑时序是否正确的仪器。目前,虽然Agilent、Tektronix 等大公司生产的高端逻辑分析仪能够实现FPGA电路的测试验证功能,但此类仪器价格...

VL16 使用8线-3线优先编码器Ⅰ实现16线-4线优先编码器 03 时序逻辑 VL21 根据状态转移表实现时序电路 VL22 根据状态转移图实现时序电路 VL23 ROM的简单实现 VL24 边沿检测 2 Verilog进阶挑战 01 序列检测 VL25 输入...

推荐文章

- Android 编译so文件 MP4V2_android下编译mp4v2-程序员宅基地

- 通讯录Contact_02_contact文件内容-程序员宅基地

- Qt笔记(四十二)之QZXing的编译 配置 使用_qzxingfilterrunnable error:-程序员宅基地

- 关于画图软件Dia打开程序始终为英文界面的问题-程序员宅基地

- OpenCV从入门到精通实战(二)——文档OCR识别(tesseract)-程序员宅基地

- 详解avcodec_receive_packet 11_avcodec_receive_packet eagain-程序员宅基地

- OpenGL SuperBible 7th源码编译记录_superbible7-media github-程序员宅基地

- Wireshark简单使用-程序员宅基地

- MXNet 粗糙的使用指南_iou loss mxnet-程序员宅基地

- iOS对ipa包进行代码混淆《二》 ---代码混淆_ipa包混淆-程序员宅基地