”逻辑门设计“ 的搜索结果

大数据-算法-可重用可组合的转录逻辑门设计.pdf

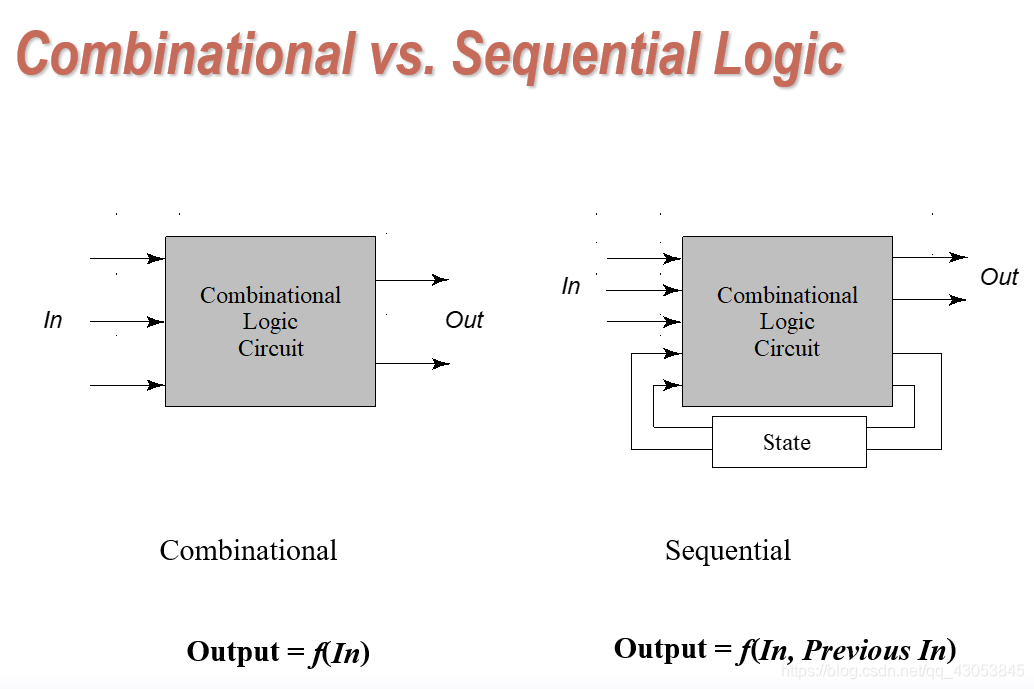

数字逻辑理论——组合电路

标签: 数字电路

04 基于DNA和限制性核酸内切酶的基本逻辑门设计.pdf

CMOS忆阻器混合逻辑门设计及其在逻辑综合中的应用,胡智鹏,尤志强,忆阻器可用于逻辑电路设计,以减小逻辑电路的面积。本文在多输入与门、或门、与非门、或非门等基本逻辑门的基础上,进一步设计出

原码转补码(逻辑门实现)

标签: FPGA

逻辑门实现的三位原码转补码,,包含原理图、波形仿真文件,大学数字电路实验内容

提出一种低功耗的仅用输入电容和CMOS反向器实现的一位全加器电路设计。该电路仅用了6个管子,从而达到降低功耗的目的。较少的管子、工作于极低电源电压以及短路电流的消除是该全加器3个主要特征。

这项研究旨在设计和组装简易的逻辑门模拟器,该逻辑门模拟器可以用作菲律宾卡拉加州立大学Cabadbaran校区的基本数字电子教学中的教学设备。 该教学设备被认为可以改善教学过程,也有助于解决学校和全国教学设备的...

逻辑计算器

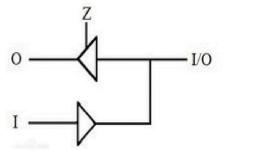

用verilog来设计逻辑门、三态门、mux等

常用逻辑门芯片测试装置研究与设计.pdf

数字电路与逻辑设计:CH2 集成逻辑门.pdf

五个模具,挑自己觉得合适舒服的用就行

数电实验仿真

数字集成电路

首先提出多数决定逻辑非门的概念和电路设计,然后提出一种基于多数决定逻辑非门的全加器电路设计。该全加器仅由输入电容和CMOS反向器组成,较少的管子、工作于极低电源电压、短路电流的消除是该全加器的三个主要特征...

基于面包板的在线逻辑门芯片测试装置设计.pdf

有时候我们搭电路时只需要实现一个...鉴于简化电路的需要我整理了一套用三极管、二极管、电阻组成的逻辑门电路,可实现2输入或3输入的 AND,OR,NAND,NOR,EXOR操作。本文列出了几种二极管和三极管组成的逻辑门电路。

【数字电路】集成逻辑门电路

标签: 数字电路

集成电路设计课件:CMOS组合逻辑门的设计:低功耗.ppt

文章目录1 用逻辑门制作出加法器1.1 半加器1.2 全加器1.3 8位加法器 1 用逻辑门制作出加法器 1.1 半加器 我们首先看下二进制加法的运算规则: 我们将加法值、进位值的真值表和异或运算、与运算的真值表进行对比: ...

集成电路设计课件:4 CMOS组合逻辑门的设计:低功耗.ppt

设计一个控制步进电动机三相六状态工作的逻辑电路。如果用1表示电机绕组导通,0表示电机绕组截止,则ABC的状态转换图如下所示。M为输入控制变量,当M=1时正转,M=0时反转。(逻辑门实现,非代码)

集成电路设计课件:4-12 CMOS组合逻辑门的设计:低功耗.ppt

推荐文章

- 1N5819-ASEMI轴向肖特基二极管1N5819-程序员宅基地

- 把maven的setting配置文件改为需要jdk版本_<profile> <id>jdk-1.4</id> <activation> <jdk>1.4</-程序员宅基地

- 使用matlab进行DBscan聚类_dbscan聚类分析图用什么软件-程序员宅基地

- 探秘技术新星:BBS_admin - 一个现代化的论坛后台管理系统-程序员宅基地

- 【译】JavaScript 开发者年度调查报告-程序员宅基地

- 神仙级渗透测试入门教程(非常详细),从零基础入门到精通,从看这篇开始!_网络渗透技术自学-程序员宅基地

- 多个protocbuf版本切换_protobuf调整版本-程序员宅基地

- msf+cobaltstrike联动(一):把msf的session发给cobaltstrike-程序员宅基地

- C语言--编写程序,输入一个整数,判断它能否被3,5,7整除_编程序实现功能:输入一个整数,判断其是否能同时被3、5、7整除。能被整除则输出“y-程序员宅基地

- 数据技术之Hadoop(HFDS文件系统)-程序员宅基地